NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

157 / 205

Field Description

2

PWU

PWU – Power Wake-up Module Reset Bit

The PWU bit indicates a PWU reset has been detected.

0 = PWU reset not detected; Result of power-on reset; Existing state retained from resets of Stop1 exit,

low voltage detection, external pin, COP, PWU, illegal opcode, illegal address, soft reset, and back-ground

debugger.

1 = PWU reset detected.

1

LVR

LVR — Low Voltage Reset Bit

The LVR bit indicates a low voltage reset has been detected.

0 = Low voltage reset not detected; Existing state retained from resets of Stop1 exit, low voltage detection,

external pin, COP, PWU, illegal opcode, illegal address, soft reset, and back-ground debugger.

1 = Low voltage reset detected; Result of power-on reset.

0

SOFT

SOFT – Soft Reset Bit

0 = Soft reset not detected or result of subsequent read after initial read; Result of power-on reset; Existing

state retained from resets of Stop1 exit, low voltage detection, external pin, COP, PWU, illegal opcode,

illegal address, soft reset, and back-ground debugger.

1 = Soft reset detected; Result of initial read in the case the Soft Reset function had been triggered.

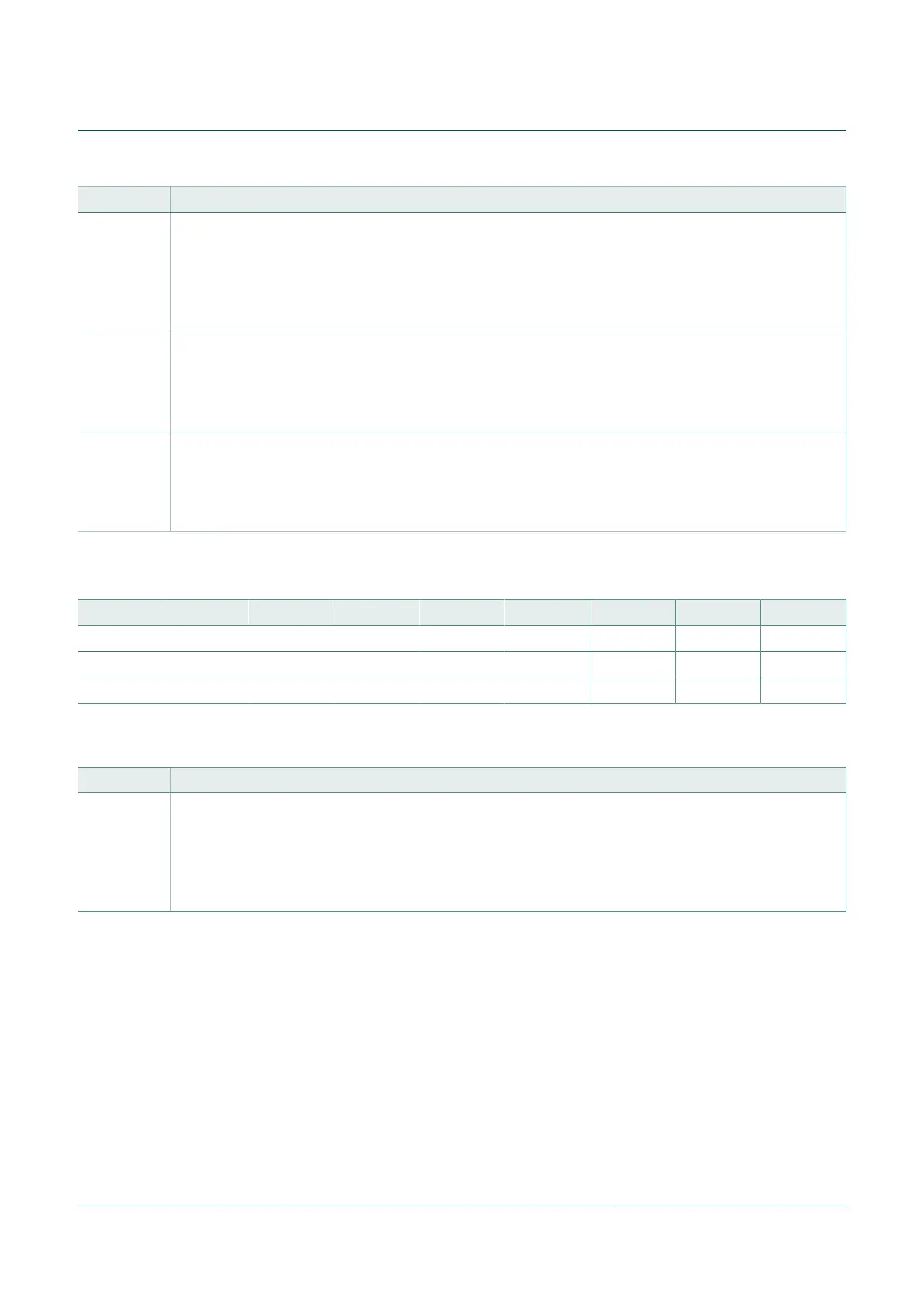

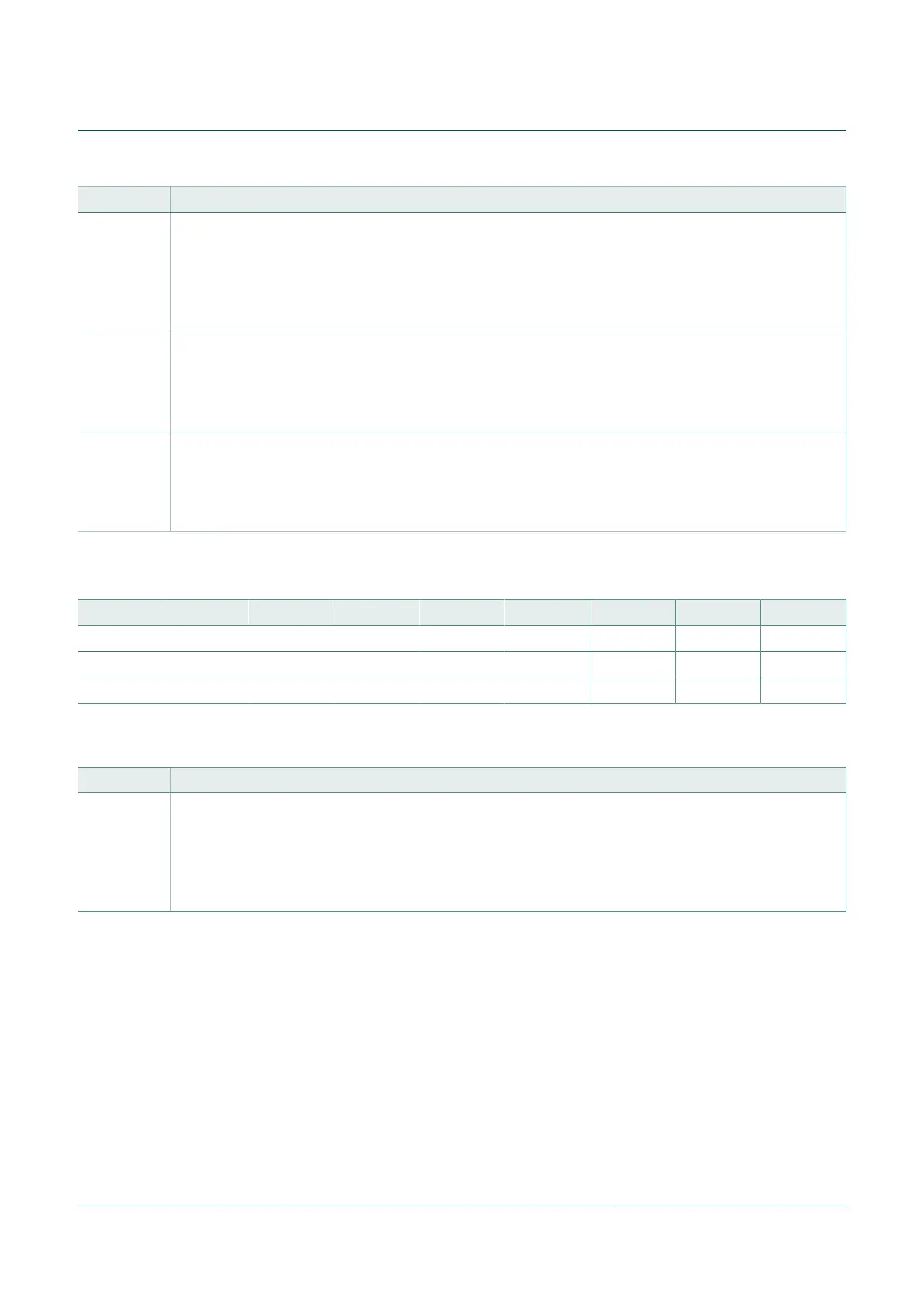

10.22.3.2 SIM control register (SIMC)

Table 162. SIM control register (SIMC) (address $1801)

Bit 7 6 5 4 3 2 1 0

R 0 0 0 0 0 0 0 —

W — — — — — — — BDFR

Reset ($00) 0 0 0 0 0 0 0 0

Table 163. SIMC register field descriptions

Field Description

0

BDFR

BDFR — Background Debug Forced Reset Bit

While in background debug mode, a write to the BDFR bit forces a system reset. Resetting by this method

is directly controlled by the user and does not result in the setting of any bits of the SIMRS register unless

another reset source becomes pending on the same cycle.

0 = Do not force system reset; Result of Reset

1 = Force a system reset.

10.22.3.3 SIM option 1 register (SIMOPT1)

A true power-on reset (POR) is caused by first applying power to chip pins or remove

and re-apply power to pins. Whereas exit of a Stop mode is not a POR. The bits COPE,

COPCLKS and STOPE of SIMOPT1 register are write-once bits. The bits RFEN, SPIEN,

and BKGDPE can be written anytime.

Loading...

Loading...