Lesson 1 – Analog Clock Domain Description

372

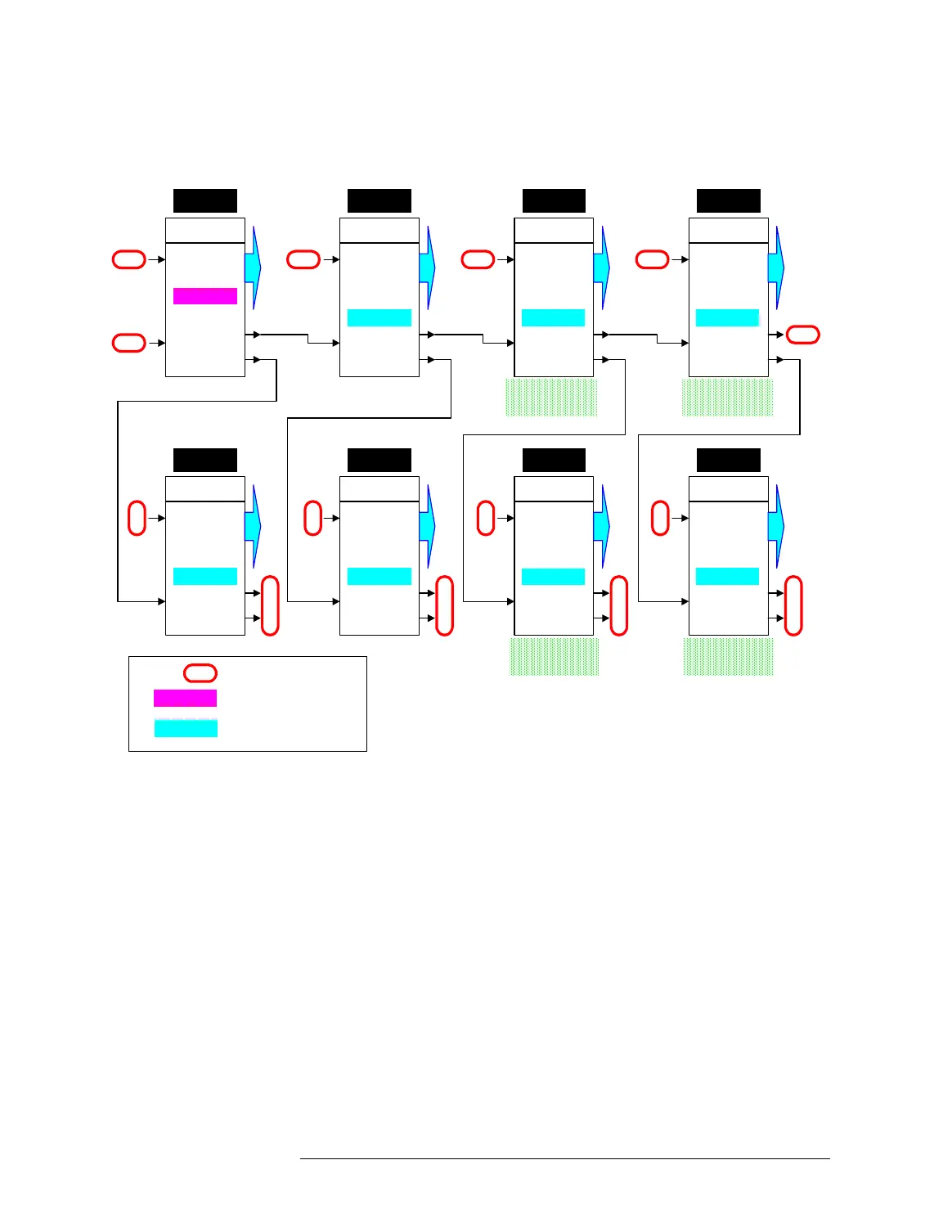

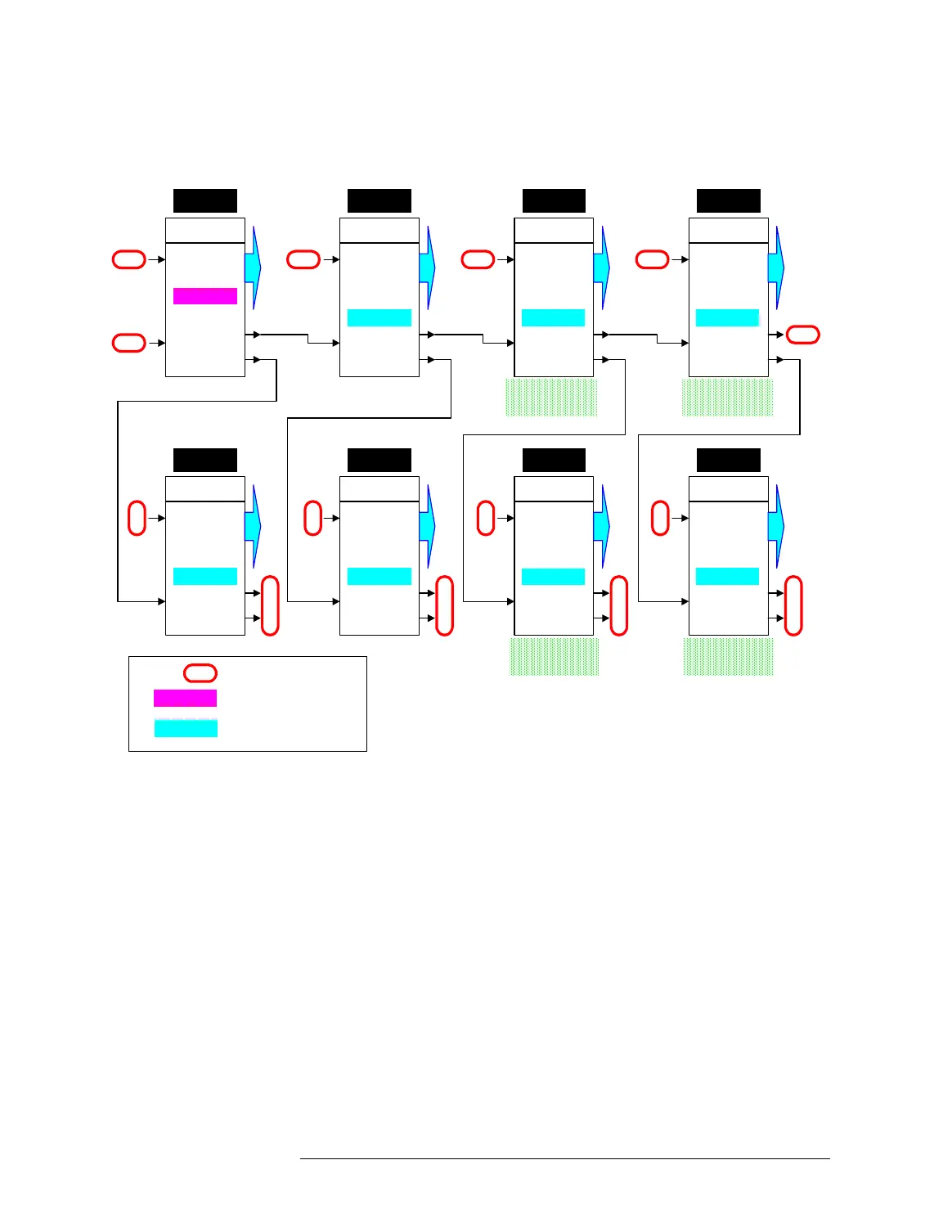

Clock Distribution 1024 Testhead (no AMC, Digital Domain only)

In the figure above, the clock board in card cage 5 generates the

clock signal (master). The signal is distributed via Ring A and Ring

B to all other clock boards (slaves).

Note: Although named Ring, the signal lines A and B are not

closed loops.

Master

RING A

RING B

Ring

Ext.

C. Cage 5

NC

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 3

NC

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 8

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 2

SLOTS

NC

RingRing

Ring

Slave

RING A

RING B

Ring

Ext.

C. Cage 1

NC

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 7

NC

NC

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 4

SLOTS

Slave

RING A

RING B

Ring

Ext.

C. Cage 6

SLOTS

RingRing

Ring

NC

NC

NC

Ring

NC

Local PLL

NC NC

NC

NC

NC

Not Connected

Local PLL

Ring

Clock generated by PLL

Clock forwarded from the

previous clock board

Analog Card Cage Analog Card Cage

Analog Card Cage Analog Card Cage

Loading...

Loading...