444

8331B–AVR–03/12

Atmel AVR XMEGA AU

When EEPROM memory mapping is enabled, loading a data byte into the EEPROM page buffer

can be performed through direct or indirect store instructions. Only the least-significant bits of

the EEPROM address are used to determine locations within the page buffer, but the complete

memory mapped EEPROM address is always required to ensure correct address mapping.

Reading from the EEPROM can be done directly using direct or indirect load instructions. When

a memory mapped EEPROM page buffer load operation is performed, the CPU is halted for two

cycles before the next instruction is executed.

When the EEPROM is memory mapped, the EEPROM page buffer load and EEPROM read

functionality from the NVM controller are disabled.

33.11.5 NVM EEPROM Commands

The NVM flash commands that can be used for accessing the EEPROM through the NVM con-

troller are listed in Table 33-4.

For self-programming of the EEPROM, the trigger for action-triggered commands is to set the

CMDEX bit in the NVM CTRLA register (CMDEX). The read-triggered command is triggered by

reading the NVM DATA0 register (DATA0).

The Change Protected column indicates whether the trigger is protected by the configuration

change protection (CCP) during self-programming or not. CCP is not required for external pro-

gramming. The last two columns show the address pointer used for addressing and the

source/destination data register.

Section 33.11.5.1 on page 444 through Section 33.11.5.7 on page 446 explain in detail the algo-

rithm for each EEPROM operation.

33.11.5.1 Load EEPROM Page Buffer

The load EEPROM page buffer command is used to load one byte into the EEPROM page

buffer.

1. Load the NVM CMD register with the load EEPROM page buffer command.

2. Load the NVM ADDR0 register with the address to write.

3. Load the NVM DATA0 register with the data to write. This will trigger the command.

Repeat steps 2-3 until the arbitrary number of bytes are loaded into the page buffer.

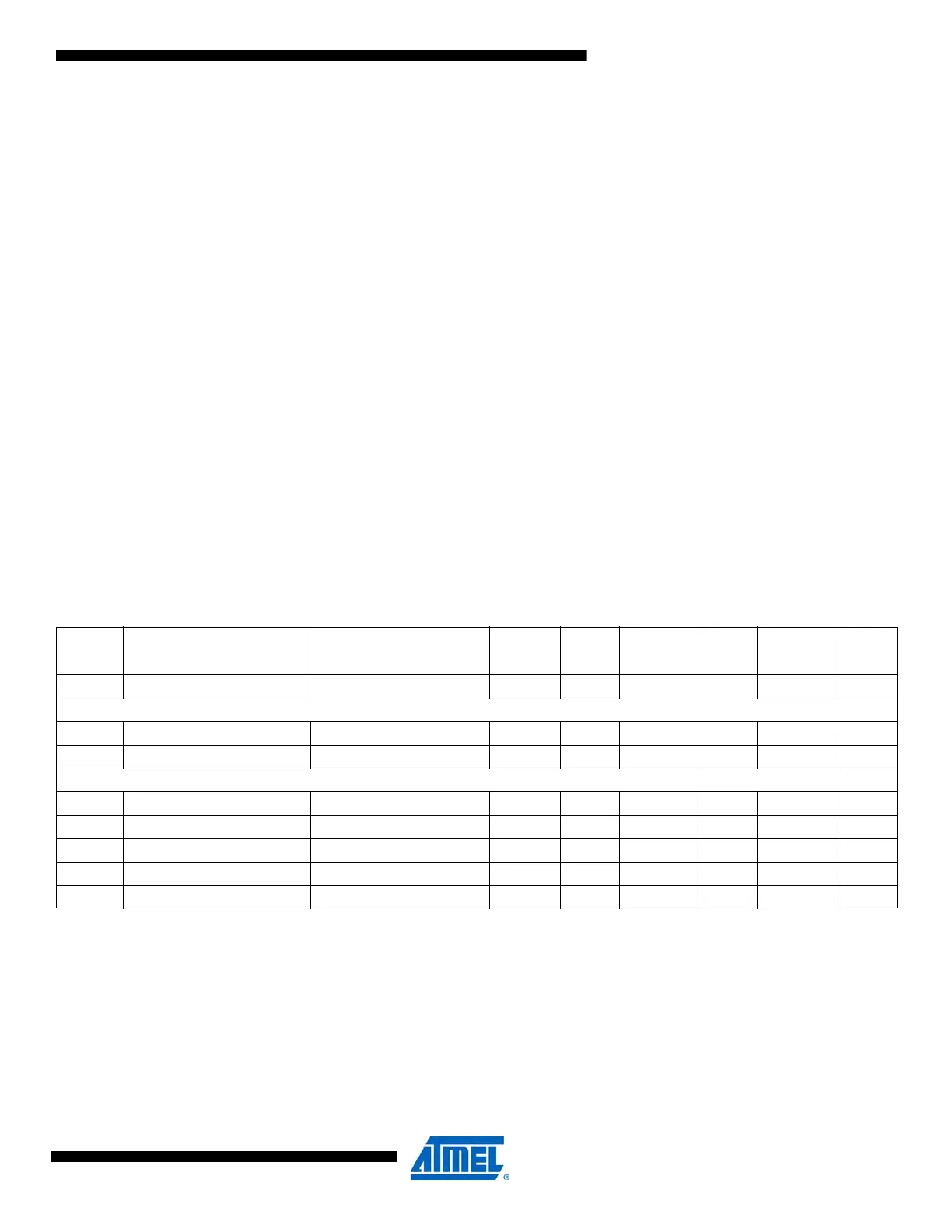

Table 33-4. EEPROM self-programming commands.

CMD[6:0] Group Configuration Description Trigger

CPU

Halted

Change

Protected

NVM

Busy

Address

Pointer

Data

Registe

r

0x00 NO_OPERATION No operation - - - - - -

EEPROM Page Buffer

0x33 LOAD_EEPROM_BUFFER Load EEPROM page buffer DATA0 N Y N ADDR DATA0

0x36 ERASE_EEPROM _BUFFER Erase EEPROM page buffer CMDEX N Y Y - -

EEPROM

0x32 ERASE_EEPROM_PAGE Erase EEPROM page CMDEX N Y Y ADDR -

0x34 WRITE_EEPROM_PAGE Write EEPROM page CMDEX N Y Y ADDR -

0x35 ERASE_WRITE_EEPROM_PAGE Erase and write EEPROM page CMDEX N Y Y ADDR -

0x30 ERASE_EEPROM Erase EEPROM CMDEX N Y Y - -

0x06 READ_EEPROM Read EEPROM CMDEX N Y N ADDR DATA0

Loading...

Loading...