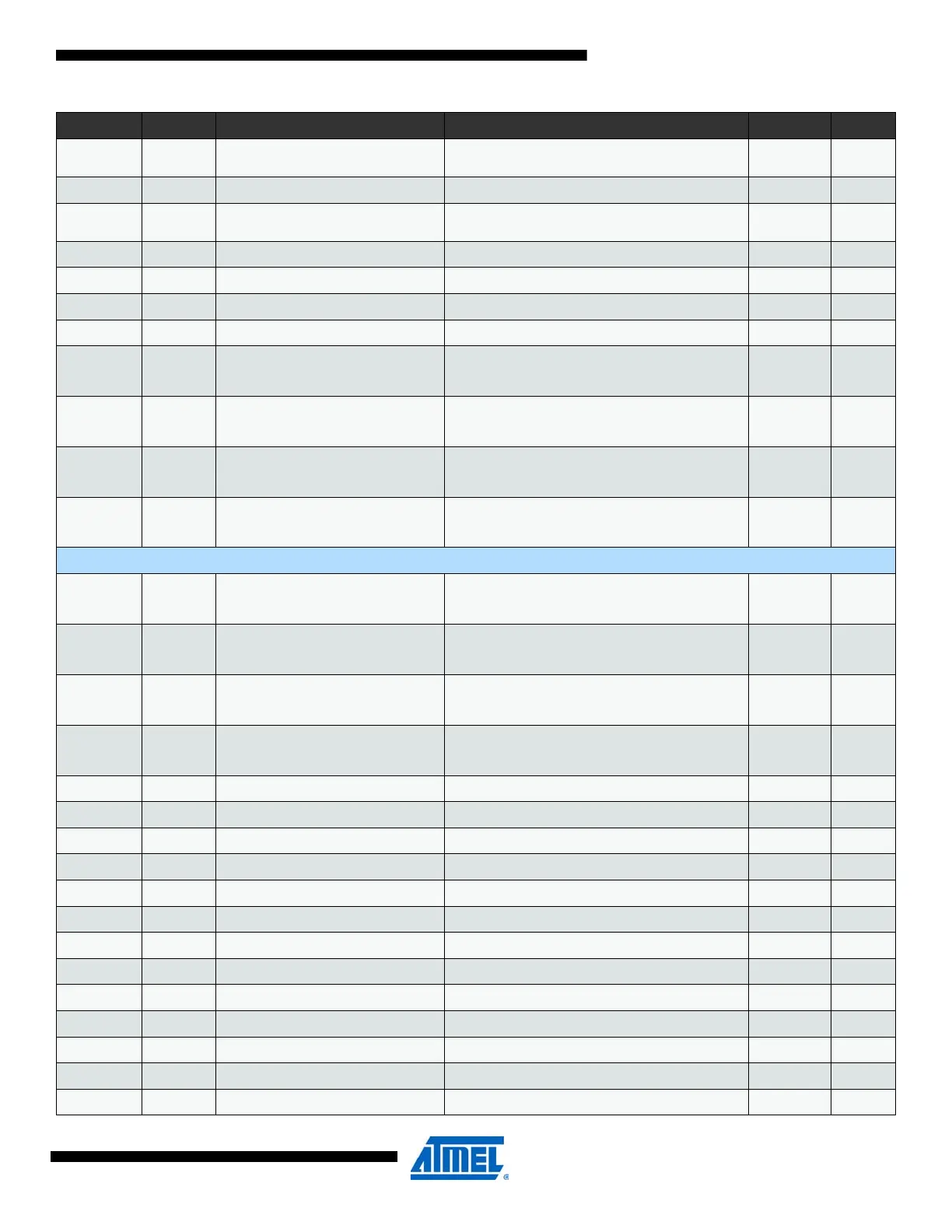

459

8331B–AVR–03/12

Atmel AVR XMEGA AU

ELPM Rd, Z+ Extended Load Program Memory and Post-

Increment

Rd

Z

←

←

(RAMPZ:Z),

Z + 1

None 3

SPM Store Program Memory (RAMPZ:Z) ← R1:R0 None -

SPM Z+ Store Program Memory and Post-Increment

by 2

(RAMPZ:Z)

Z

←

←

R1:R0,

Z + 2

None -

IN Rd, A In From I/O Location Rd ← I/O(A) None 1

OUT A, Rr Out To I/O Location I/O(A) ← Rr None 1

PUSH Rr Push Register on Stack STACK ← Rr None 1

(1)

POP Rd Pop Register from Stack Rd ← STACK None 2

(1)

XCH Z, Rd Exchange RAM location Tem p

Rd

(Z)

←

←

←

Rd,

(Z),

Te mp

None 2

LAS Z, Rd Load and Set RAM location Tem p

Rd

(Z)

←

←

←

Rd,

(Z),

Te mp v ( Z )

None 2

LAC Z, Rd Load and Clear RAM location Te mp

Rd

(Z)

←

←

←

Rd,

(Z),

($FFh – Rd) • (Z)

None 2

LAT Z, Rd Load and Toggle RAM location Te mp

Rd

(Z)

←

←

←

Rd,

(Z),

Te mp ⊕ (Z)

None 2

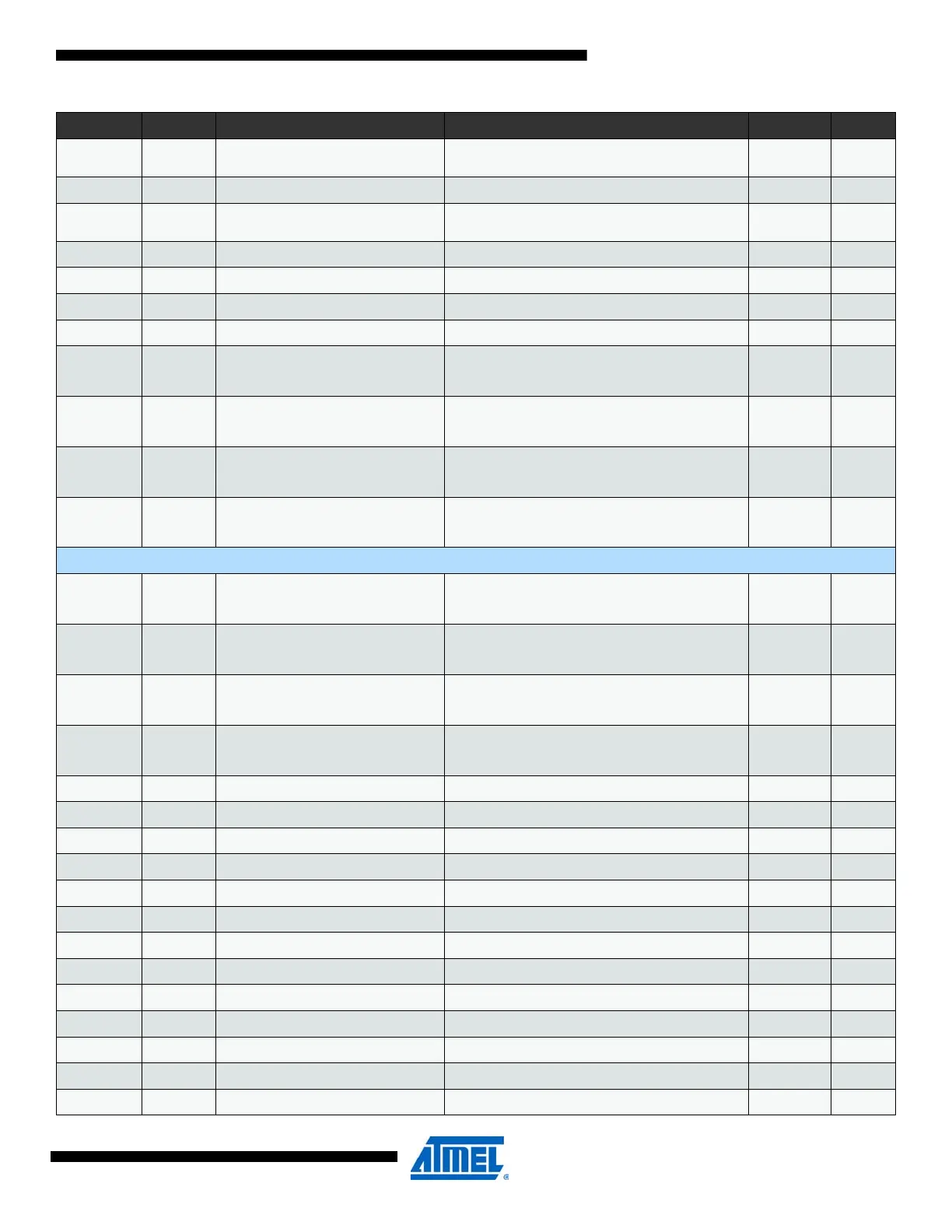

Bit and bit-test instructions

LSL Rd Logical Shift Left Rd(n+1)

Rd(0)

C

←

←

←

Rd(n),

0,

Rd(7)

Z,C,N,V,H 1

LSR Rd Logical Shift Right Rd(n)

Rd(7)

C

←

←

←

Rd(n+1),

0,

Rd(0)

Z,C,N,V 1

ROL Rd Rotate Left Through Carry Rd(0)

Rd(n+1)

C

←

←

←

C,

Rd(n),

Rd(7)

Z,C,N,V,H 1

ROR Rd Rotate Right Through Carry Rd(7)

Rd(n)

C

←

←

←

C,

Rd(n+1),

Rd(0)

Z,C,N,V 1

ASR Rd Arithmetic Shift Right Rd(n) ← Rd(n+1), n=0..6 Z,C,N,V 1

SWAP Rd Swap Nibbles Rd(3..0) ↔ Rd(7..4) None 1

BSET s Flag Set SREG(s) ← 1 SREG(s) 1

BCLR s Flag Clear SREG(s) ← 0 SREG(s) 1

SBI A, b Set Bit in I/O Register I/O(A, b) ← 1 None 1

CBI A, b Clear Bit in I/O Register I/O(A, b) ← 0 None 1

BST Rr, b Bit Store from Register to T T ← Rr(b) T 1

BLD Rd, b Bit load from T to Register Rd(b) ← T None 1

SEC Set Carry C ← 1 C 1

CLC Clear Carry C ← 0 C 1

SEN Set Negative Flag N ← 1 N 1

CLN Clear Negative Flag N ← 0 N 1

SEZ Set Zero Flag Z ← 1 Z 1

Mnemonics Operands Description Operation Flags #Clocks

Loading...

Loading...