460

8331B–AVR–03/12

Atmel AVR XMEGA AU

Notes: 1. Cycle times for data memory accesses assume internal memory accesses, and are not valid for accesses via the external RAM interface.

2. One extra cycle must be added when accessing Internal SRAM.

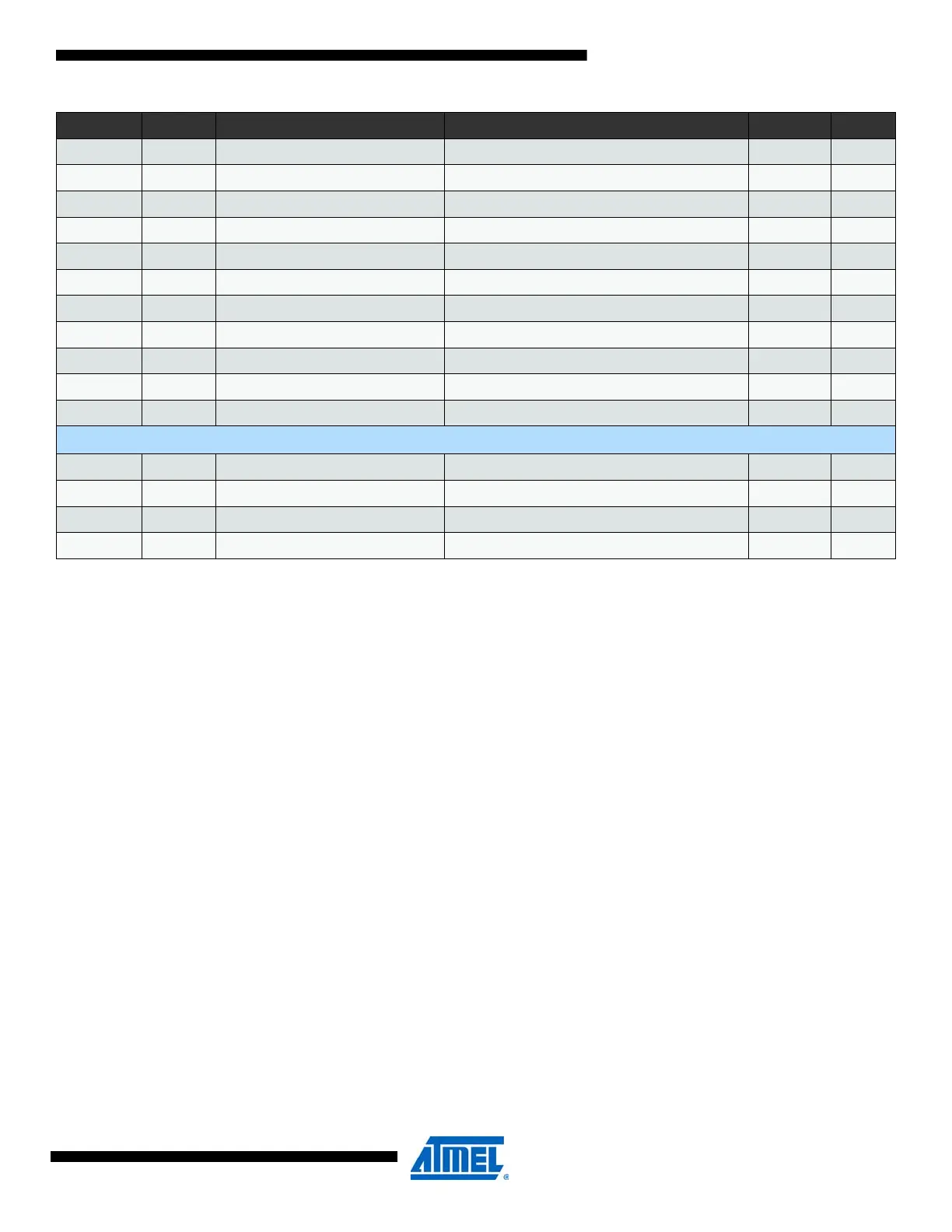

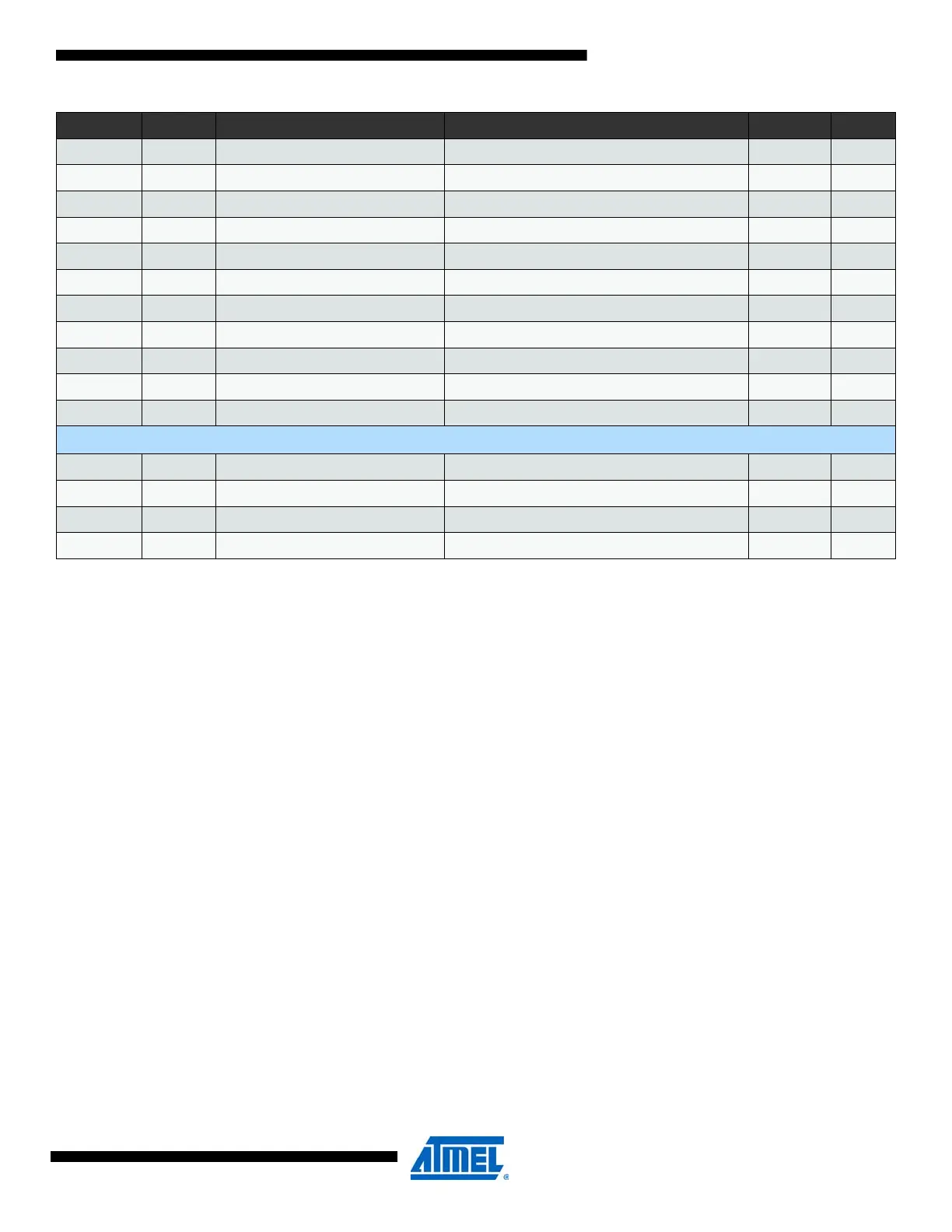

CLZ Clear Zero Flag Z ← 0 Z 1

SEI Global Interrupt Enable I ← 1 I 1

CLI Global Interrupt Disable I ← 0 I 1

SES Set Signed Test Flag S ← 1 S 1

CLS Clear Signed Test Flag S ← 0 S 1

SEV Set Two’s Complement Overflow V ← 1 V 1

CLV Clear Two’s Complement Overflow V ← 0 V 1

SET Set T in SREG T ← 1 T 1

CLT Clear T in SREG T ← 0 T 1

SEH Set Half Carry Flag in SREG H ← 1 H 1

CLH Clear Half Carry Flag in SREG H ← 0 H 1

MCU control instructions

BREAK Break (See specific descr. for BREAK) None 1

NOP No Operation None 1

SLEEP Sleep (see specific descr. for Sleep) None 1

WDR Watchdog Reset (see specific descr. for WDR) None 1

Mnemonics Operands Description Operation Flags #Clocks

Loading...

Loading...