468

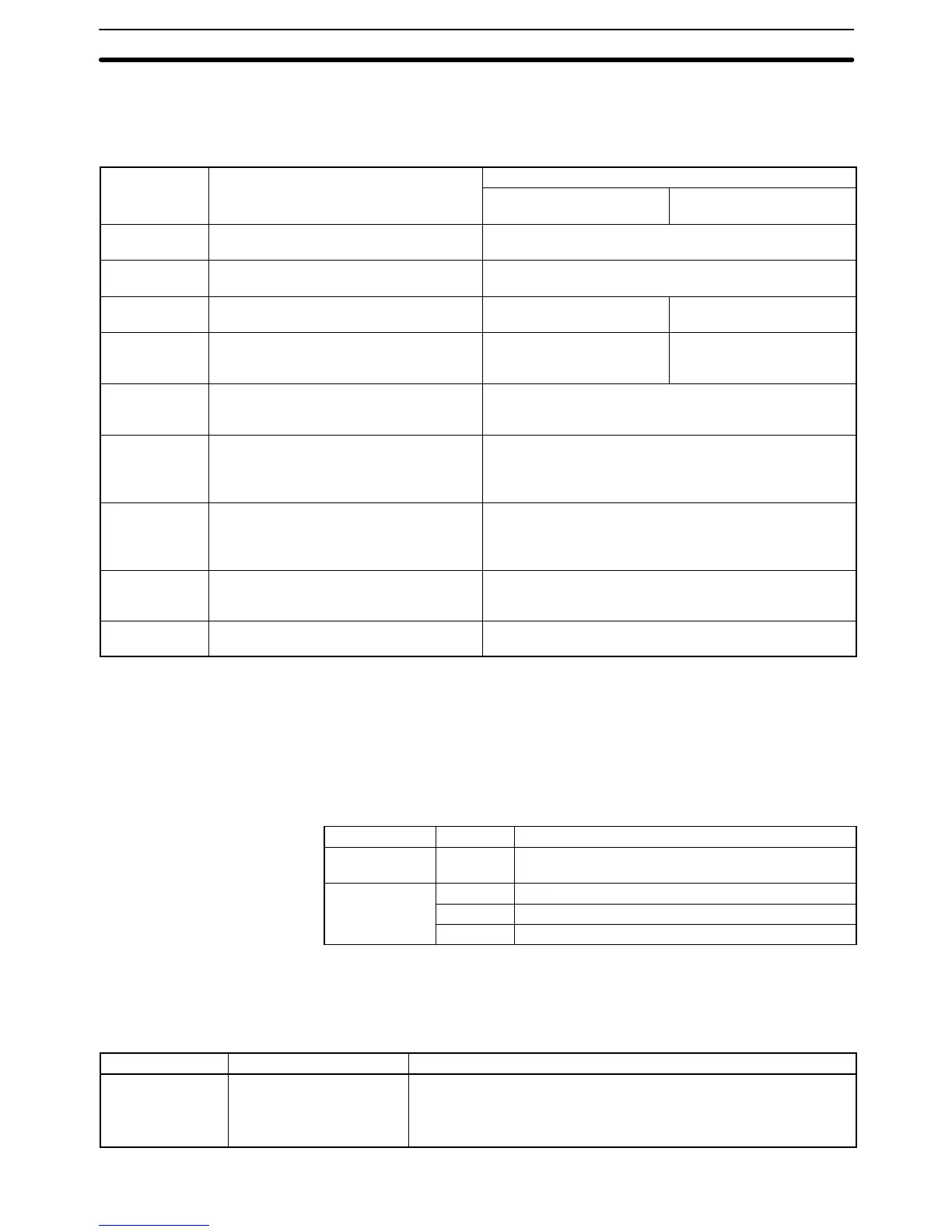

Depending on the program, the following interrupt processes might be executed

in addition to the processes detailed in the table above. The actual cycle time is

the sum of the cycle time calculated in the table above and the time required for

the processes in the table below.

Process Actions Processing time

CV500/CVM1-CPU01-EV2 CV1000/2000/

CVM1-CPU11/21-EV2

I/O interrupts I/O interrupt programs started with receipt

of interrupts from Interrupt Input Units.

Depends on the I/O interrupt programs.

Scheduled

interrupt

Scheduled interrupt program(s) started at

preset interval(s).

Depends on the scheduled interrupt program(s).

TIMH(015)

refreshing

Updates the PVs of high-speed timers in

the program every 10 ms.

12 µs + 0.8 µs per timer 10 µs + 0.7 µs per timer

Timer

refreshing

Updates the PVs of all timers in the

program every 80 ms if the cycle time

exceeds 80 ms.

10 µs + 1.1 µs per timer 8 µs + 0.9 µs per timer

I/O bus check Checks the I/O bus on the CPU,

Expansion CPU, and Expansion I/O

Racks

0.6 µs every 20 ms

SYSMAC NET

Link refreshing

The data link words allocated to SYSMAC

NET Link Units are refreshed.

Interrupt processing can occur as often as

once each cycle.

Approx. 1.4 ms + 1 µs per data link word, add 0.3 ms if

both DM and CIO are used for data links.

SYSMAC LINK

refreshing

The data link words allocated to SYSMAC

LINK Units are refreshed.

Interrupt processing can occur as often as

once each cycle.

Approx. 1.4 ms + 1 µs per data link word, add 0.3 ms if

both DM and CIO are used for data links.

SYSMAC

BUS/2

refreshing

Masters receive I/O data from Slaves.

Approx. 2.0 ms plus 1 µs per word refreshed

CPU Bus Link

refreshing

Data in the CPU Bus Link Area is

refreshed.

0.8 ms every 10 ms (when the PC is set to use the CPU

Bus Link Area in the PC Setup)

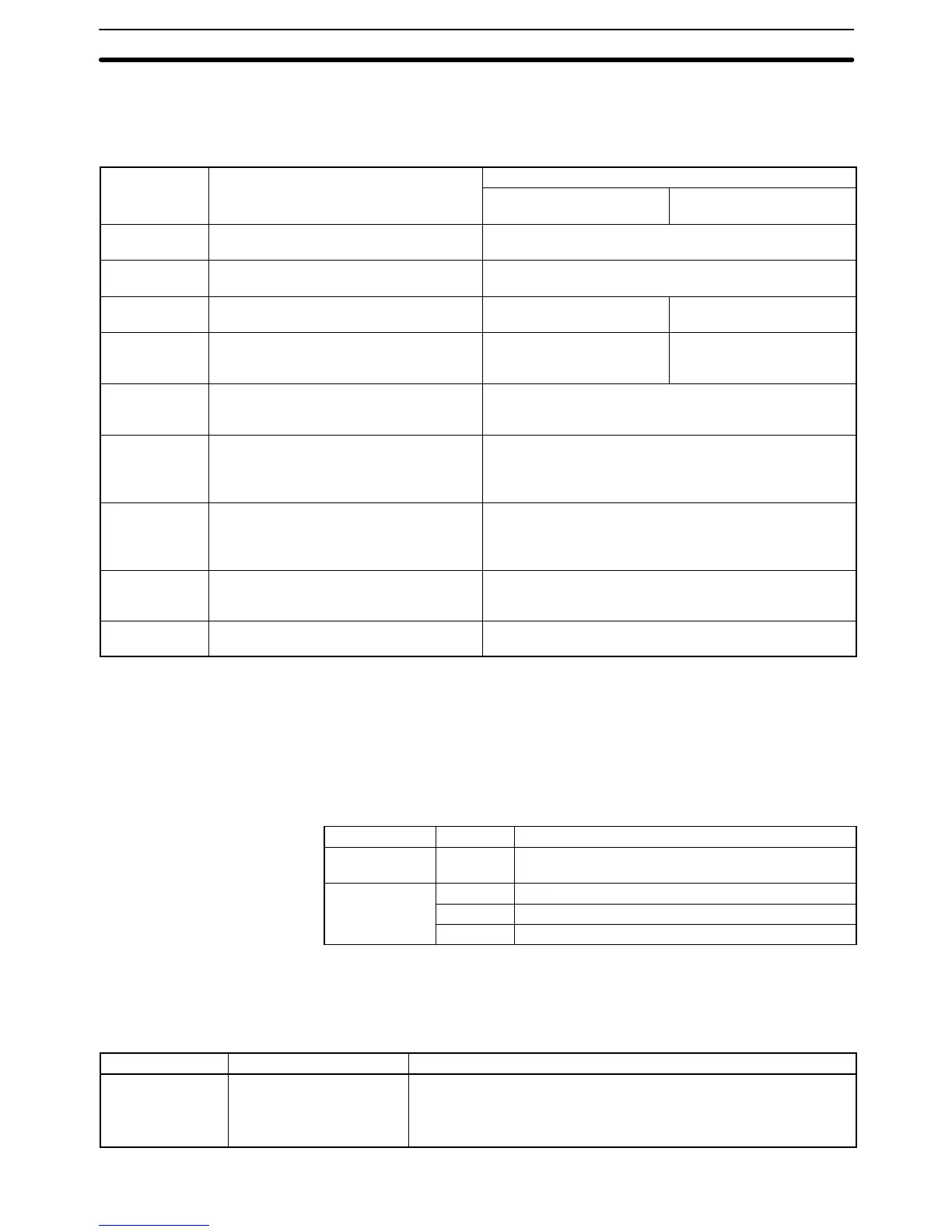

The Service Disable Bits shown in the table below are primarily used during syn-

chronous operation to reduce the cycle time; they are only effective in RUN and

MONITOR modes. The bits are OFF when the PC is first turned on, and are nor-

mally turned ON from the program.

Do not leave Service Disable Bits ON for longer than is necessary; service be-

tween the PC and the designated Unit will be stopped completely as long as the

corresponding Service Disable Bit is ON.

Word(s) Bit(s) Function

A015 00 to 15 CPU Bus Service Disable Bits (Bits 00 to 15

correspond to units #0 to #15.)

A017 03 Host Link/NT Link Service Disable Bit

04 Peripheral Service Disable Bit

05 I/O Refresh Disable Bit

6-2-3 Operations Significantly Increasing Cycle Time

The instruction trace operation described below can significantly affect the cycle

time when performed from CVSS/SSS.

Operation Effect on cycle time Precautions

Instruction trace Cycle time increased 3 to

5 times.

The cycle time will change during an instruction trace and high-speed

input signals might not be detected.

Set the maximum cycle time in the PC Setup at least 5 times higher

than its usual value.

Interrupt Processing

Service Disable Bits

Cycle Time Section 6-2

Loading...

Loading...