472

6-4 Instruction Execution Times

This following table lists the execution times for CV-series PC instructions. The

maximum and minimum execution times and the conditions which cause them

are given where relevant. When “word” is referred to in the Conditions column, it

implies the content of any word except for indirectly addressed DM words. Indi-

rectly addressed DM words, which create longer execution times when used,

are indicated by “*DM.”

Execution times for most instructions depend on whether they are executed with

an ON or an OFF execution condition. Exceptions are the ladder diagram

instructions OUT and OUT NOT, which require the same time regardless of the

execution condition. The OFF execution time for an instruction can also vary de-

pending on the circumstances, i.e., whether it is in an interlocked program sec-

tion and the execution condition for IL is OFF, whether it is between JMP(004)

and JME(005) and the execution condition for JMP(004) is OFF, or whether it is

reset by an OFF execution condition. “R,” “IL,” and “JMP” are used to indicate

these three times.

The

Words

column provides the number of words required by the instruction in

program memory. With CV-series PCs, instructions can require between one

and eight words in memory. The length of an instruction depends not only on the

instruction, but also on the operands used for the instruction. If an index register

is addressed directly or a data register is used as an operand, the instruction will

require one word less than when specifying a word address for the operand. If a

constant is designated for an instruction that uses 2-word operands, the instruc-

tion will require one word more than when specifying a word address for the op-

erand.

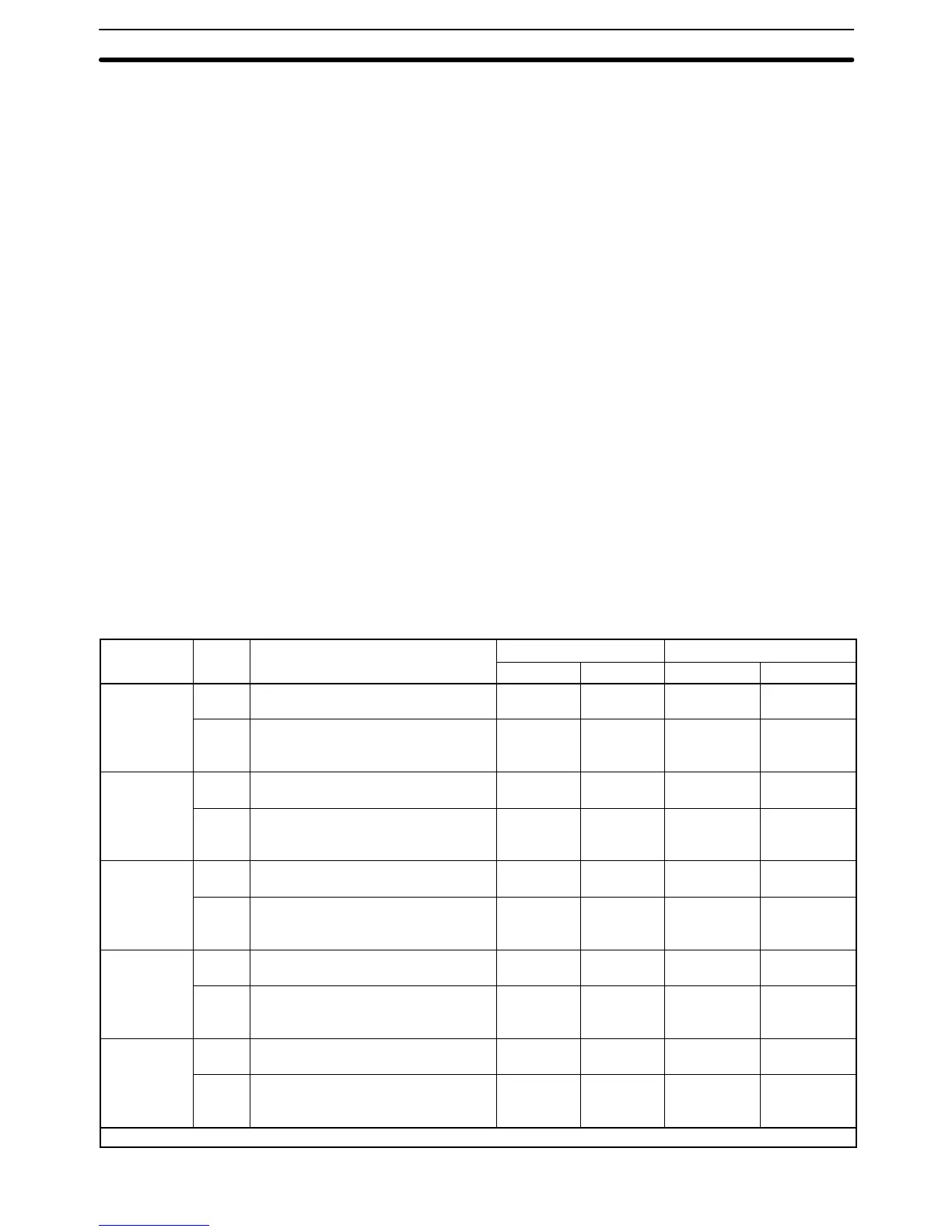

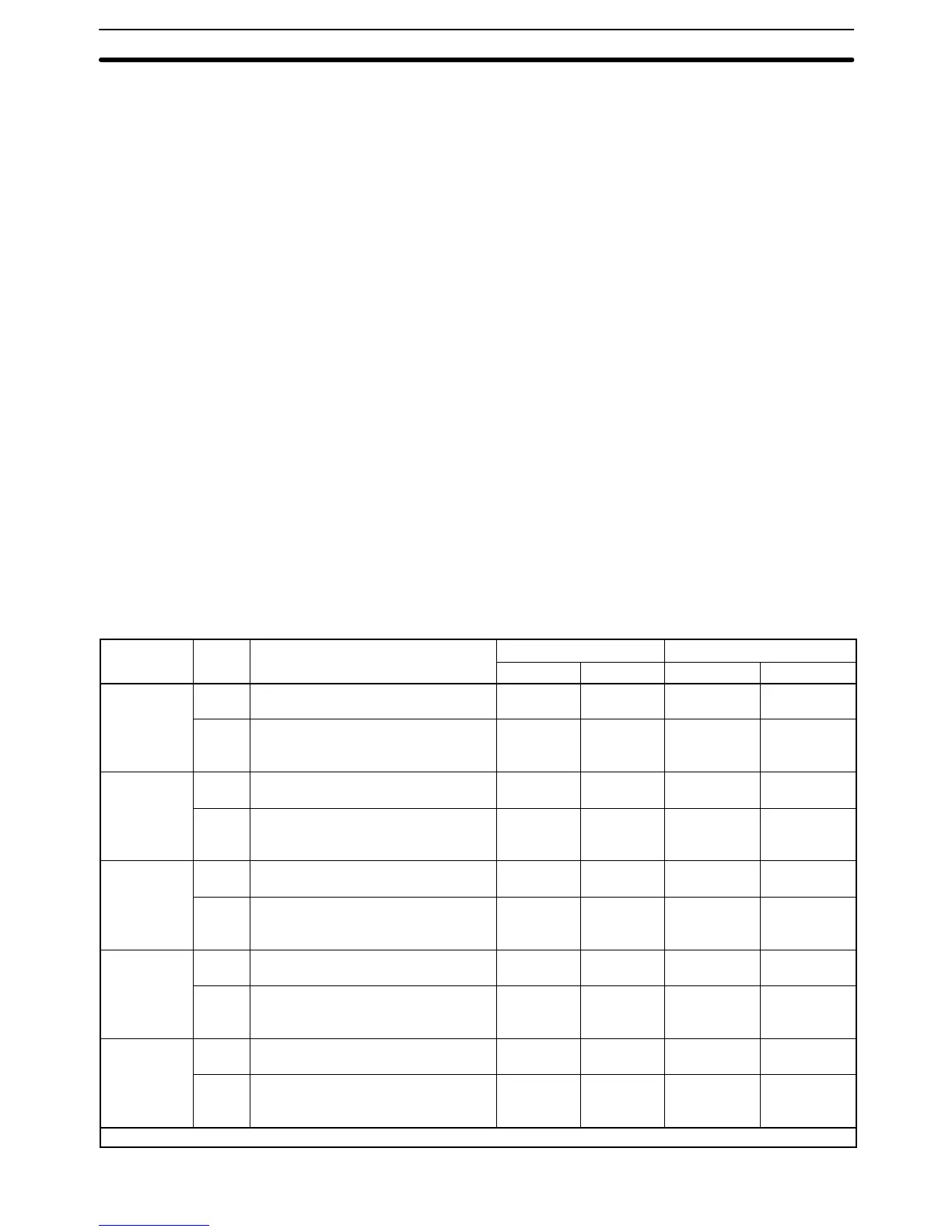

Table: Instruction Execution Times

Instruction Words Conditions

ON execution time (µs) OFF execution time (µs)

CV500* CV1000* CV500* CV1000*

LD 1 CIO 000000 to CIO 051115 for

operand

0.15 0.13 0.15 0.13

2 CIO 051200 to CIO 255515 for

operand

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

0.3

j/i: 0.75

!: 2.25

0.25

j/i: 0.625

!: 2.0

LD NOT 1 CIO 000000 to CIO 051115 for

operand

0.15 0.13 0.15 0.13

2 CIO 051200 to CIO 255515 for

operand

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

AND 1 CIO 000000 to CIO 051115 for

operand

0.15 0.13 0.15 0.13

2 CIO 051200 to CIO 255515 for

operand

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

AND NOT 1 CIO 000000 to CIO 051115 for

operand

0.15 0.13 0.15 0.13

2 CIO 051200 to CIO 255515 for

operand

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

OR 1 CIO 000000 to CIO 051115 for

operand

0.15 0.13 0.15 0.13

2 CIO 051200 to CIO 255515 for

operand

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

0.3

j/i: 0.45

!: 2.25

0.25

j/i: 0.375

!: 2.0

*Note: CV500 = CV500 or CVM1-CPU01-EV2; CV1000 = CV1000, CV2000, or CVM1-CPU11/21-EV2

Instruction Execution Times Section 6-4

Loading...

Loading...