260

ABOV Semiconductor Co., Ltd.

11.13.19 USI0/1 Asynchronous Data Reception

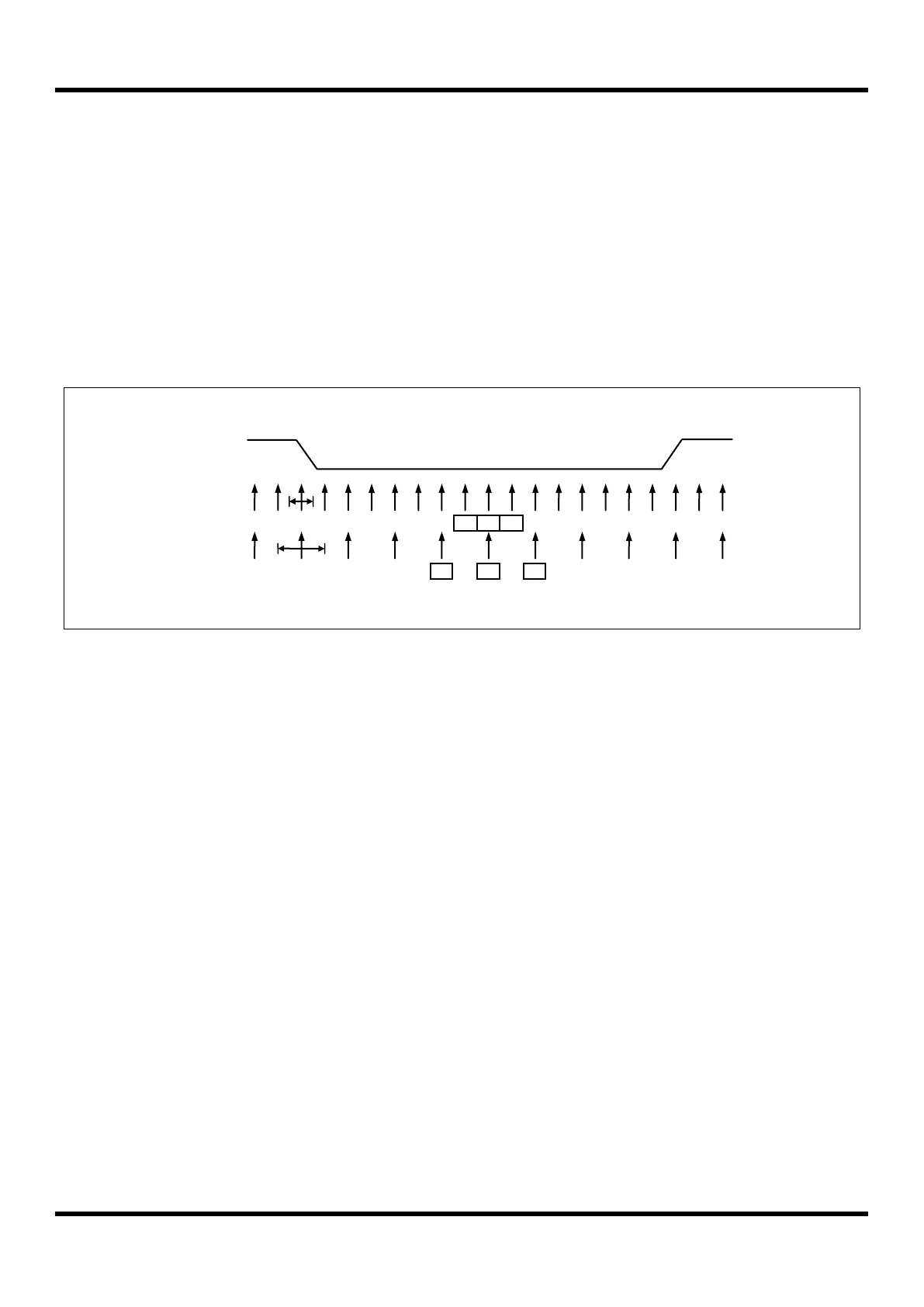

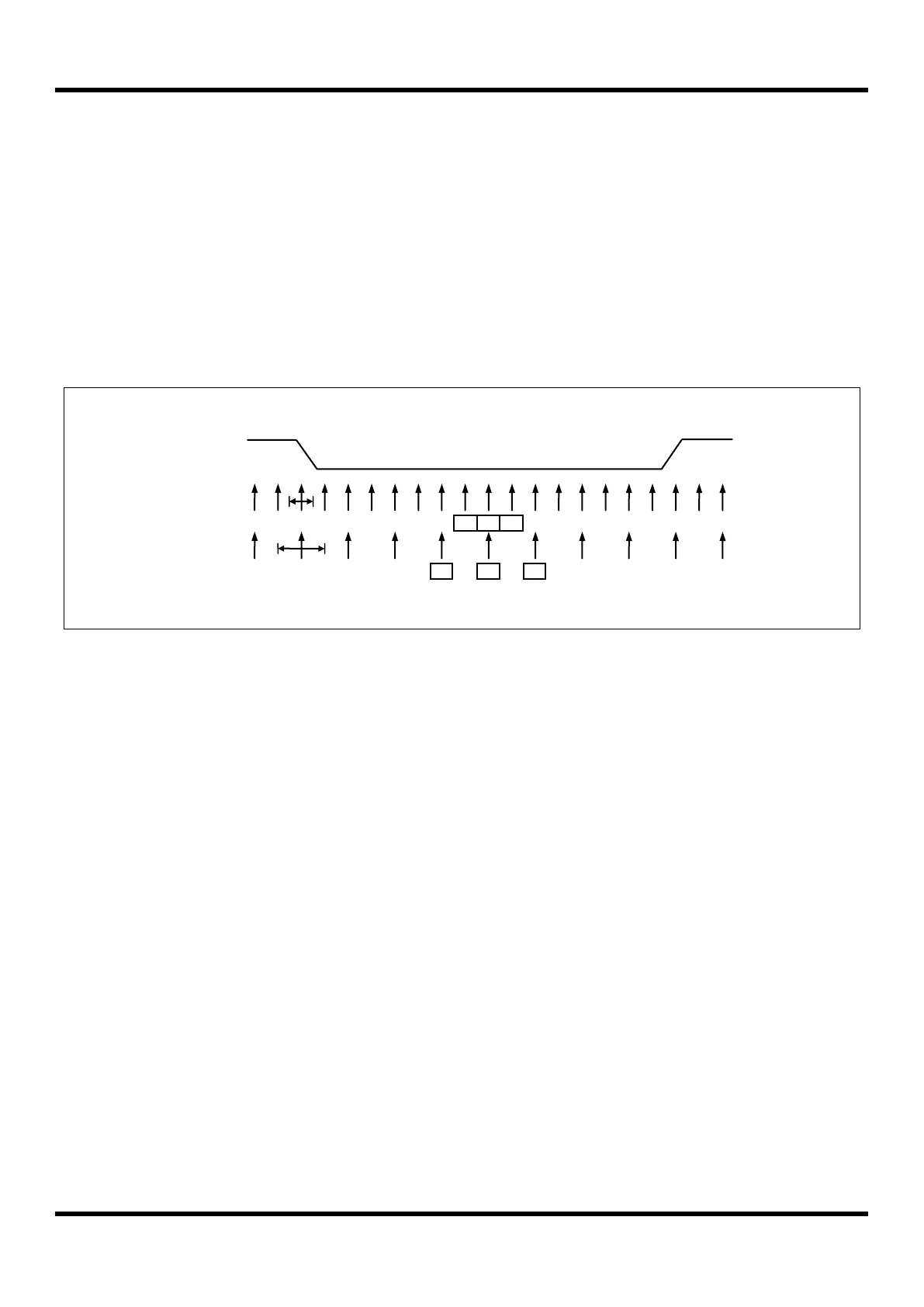

To receive asynchronous data frame, the UART includes a clock and data recovery unit. The clock recovery logic is

used for synchronizing the internally generated baud-rate clock to the incoming asynchronous serial frame on the

RXDn pin.

The data recovery logic samples and low pass filters the incoming bits and this removes the noise of RXDn pin.

The next figure illustrates the sampling process of the start bit of an incoming frame. The sampling rate is 16 times of

the baud-rate in normal mode and 8 times the baud-rate for double speed mode (DBLSn=1). The horizontal arrows

show the synchronization variation due to the asynchronous sampling process. Note that larger time variation is

shown when using the double speed mode.

Figure 11.66 Asynchronous Start Bit Sampling (USIn, where n = 0 and 1)

Loading...

Loading...