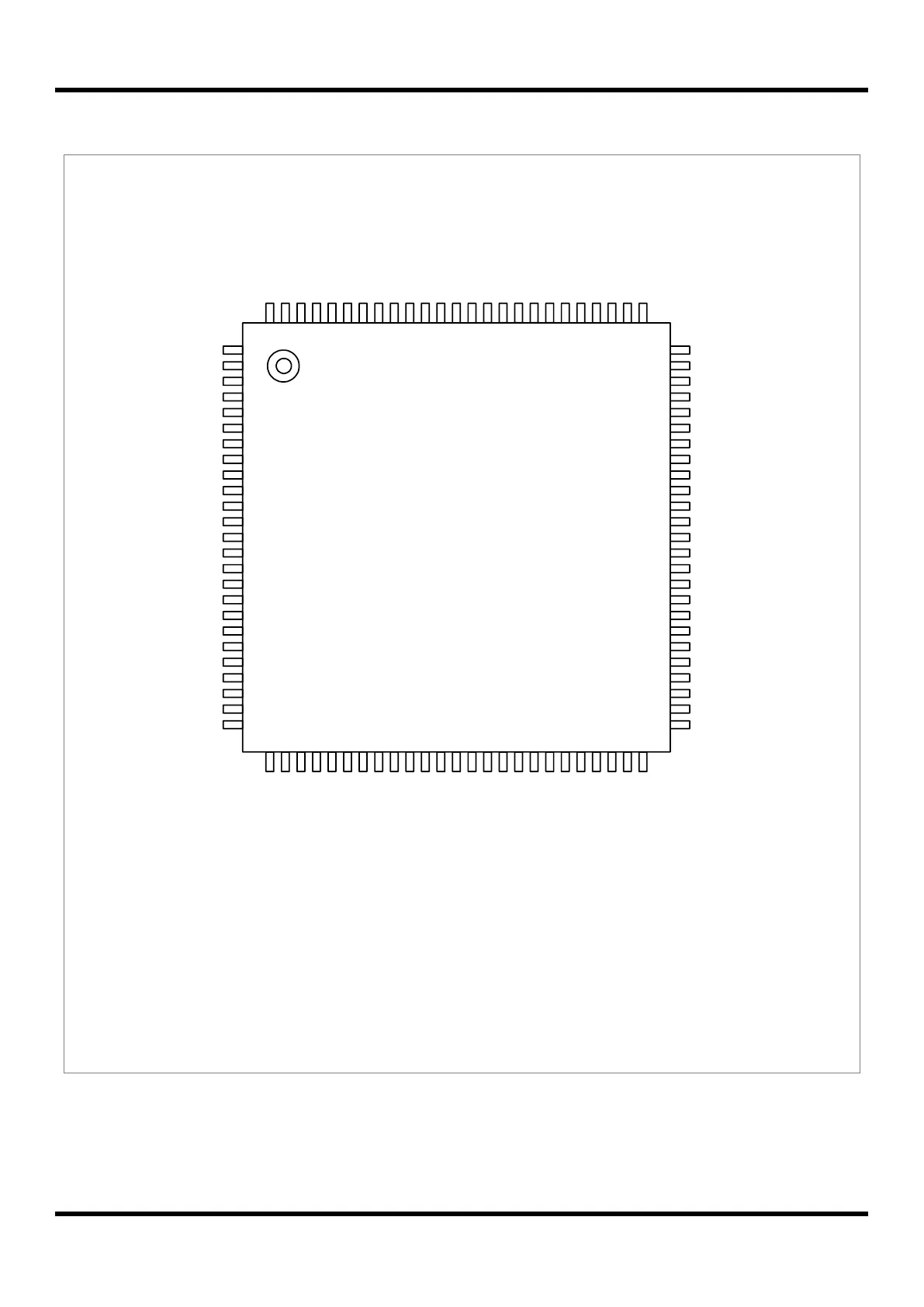

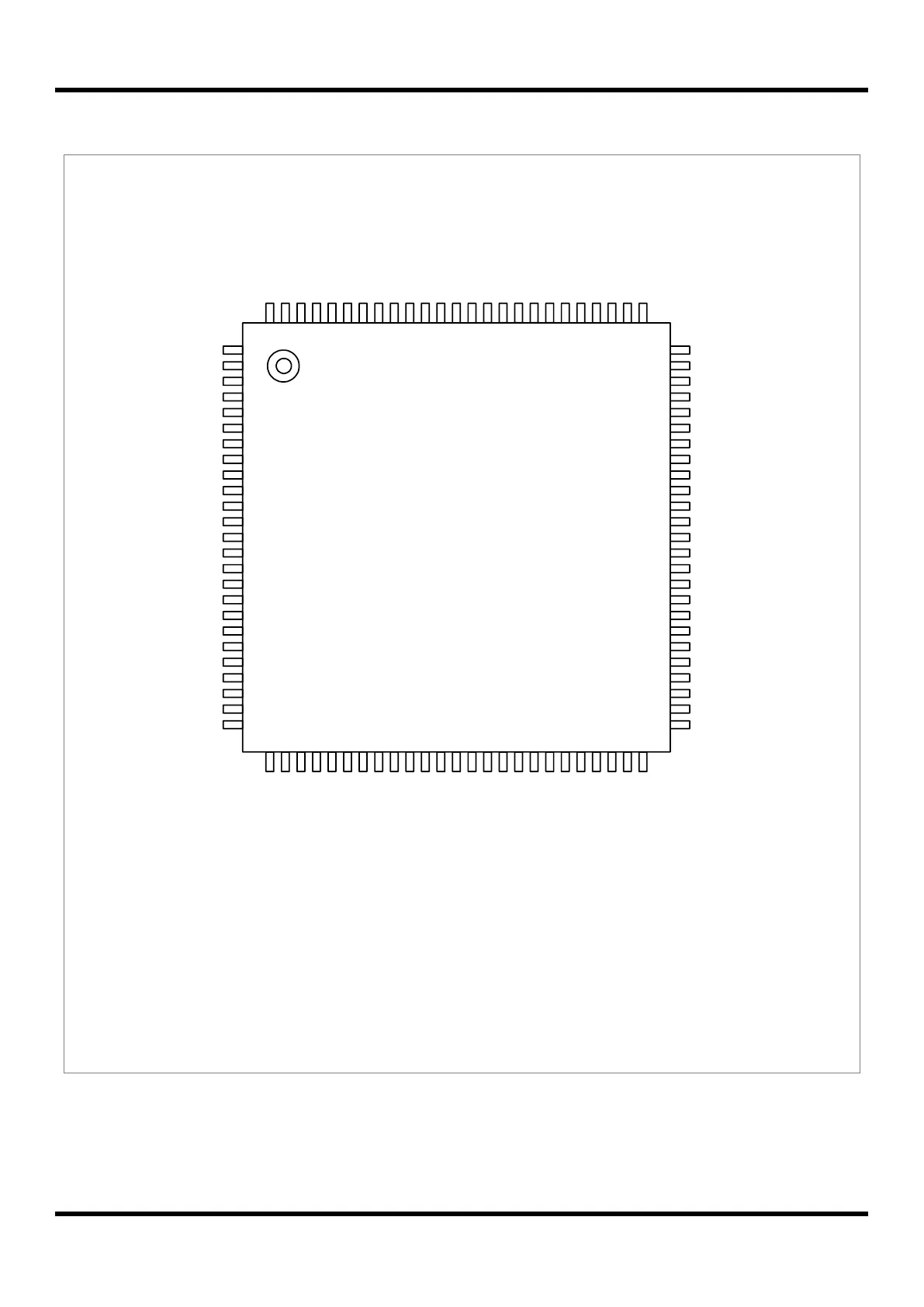

3. Pin assignment

MC97F60128L

(100LQFP-1414)

1

2

26

27

8

9

15

16

3

4

5

6

7

28

29

30

31

37

38

39

40

41

75

74

68

67

61

60

73

72

71

70

69

100

99

98

97

96

95

94

93

92

91

90

17

18

24

25

19

20

21

22

23

42

43

44

45

46

47

48

49

50

59

58

52

51

57

56

55

54

53

89

88

87

81

80

79

78

77

76

P00/AN0/EINT0/BLNK

P01/AN1/EINT1

P04/AN4/EINT4

P05/AN5/EINT5

P06/AN6/EINT6

P02/AN2/EINT2

P03/AN3/EINT3

RUNFLAG

AVSS

RESETB

LPF

VREG

VSS1

SXIN

SXOUT

VDD1

P17/XOUT

P16/XIN

P07/AN7/EINT7

AVREF

P62/AN8/EINT17/T7O

P64/AN10/TXD2

P63/AN9/EC7/DAC

P61/EINT18/T8O/PWM8AA

P60/SEG0/PWM8AB

P74/COM3

P73/SEG4/VLC0/PWM8CB

P72/SEG3/VLC1/PWM8CA

P71/SEG2/VLC2/PWM8BB

P70/SEG1/VLC3/PWM8BA

P65/AN11/RXD2

P77/COM0

P75/COM2

P76/COM1

P80/SEG10

P81/SEG11

P85/SEG15

P84/SEG14

P83/SEG13

P82/SEG12

P87/SEG17

P86/SEG16

P40/SEG29/EC0

PB2/SEG28

P52/SEG20/RXD3

P51/SEG19/TXD4

P54/SEG22/SS1

P53/SEG21/TXD3

P56/SEG24/TXD1/SDA1/MOSI1

P55/SEG23/SCK1

P50/SEG18/RXD4

P41/SEG30/EC1

P46/SEG35/BUZO

P45/SEG34/EINT12/T2O/PWM2O

P42/SEG31/EC2

P44/SEG33/EINT11/T1O/PWM1O

P43/SEG32/EINT10/T0O/PWM0O

P31/SEG38/TXD0/SDA0/MOSI0

P30/SEG37/SCK0

P47/SEG36/SS0

P11/SEG59/EINT14/T4O/PWM4O

P10/SEG58/EINT13/T3O/PWM3O/EXTSP2

P27/COM7/SEG52/EC4/EXTSP1

P26/COM6/SEG51/EC3/EXTSP0

P25/COM5/SEG50/TRIG

P24/COM4/SEG49/PWMOUT

P23/SEG48/(T3O/PWM3O/EXTSP2)

P13/SEG61/EINT16/T6O/PWM6O

P12/SEG60/EINT15/T5O/PWM5O

P15/SEG63/EINT9/EC6/DSDA

P14/SEG62/EINT8/EC5/DSCL

P36/SEG43/SS2/CSB2

P35/SEG42/SCK2

P20/SEG45/MOSI3

P37/SEG44/MISO3/LDACB3

P22/SEG47/SS3/CSB3

P21/SEG46/SCK3

P34/SEG41/MOSI2

P33/SEG40/MISO2/LDACB2

P32/SEG39/RXD0/SCL0/MISO0

13

14

10

11

12

63

62

66

65

64

P90/AN12/EINTA

P91/AN13/EINTB

P92/AN14/EINTC

P93/EINTD

P94/EINTE

P57/SEG25/RXD1/SCL1/MISO1

VSS2

VDD2

PB1/SEG27

PB0/SEG26

32

33

34

35

36

PA1/SEG54/EINTG

PA0/SEG53/EINTF

PA3/SEG56/EINTI

PA2/SEG55/EINTH

PA4/SEG57/EINTJ

86

85

84

83

82

PD0/SEG5

PD1/SEG6

PD4/SEG9

PD3/SEG8

PD2/SEG7

NOTE)

1. On On-Chip Debugging, ISP uses P1[5:4] pin as DSDA, DSCL.

2. The pin in parentheses can be configured by software control.

Loading...

Loading...