40

ABOV Semiconductor Co., Ltd.

7.14 UART0/1/2/3/4 Characteristics

(T

A

=-40°C ~ +85°C, VDD=1.8V ~ 5.5V, f

XIN

=11.1MHz)

Serial port clock cycle time

Output data setup to clock rising edge

Clock rising edge to input data valid

Output data hold after clock rising edge

Input data hold after clock rising edge

Serial port clock High, Low level width

Table 7-15 UART0/1/2/3/4 Characteristics

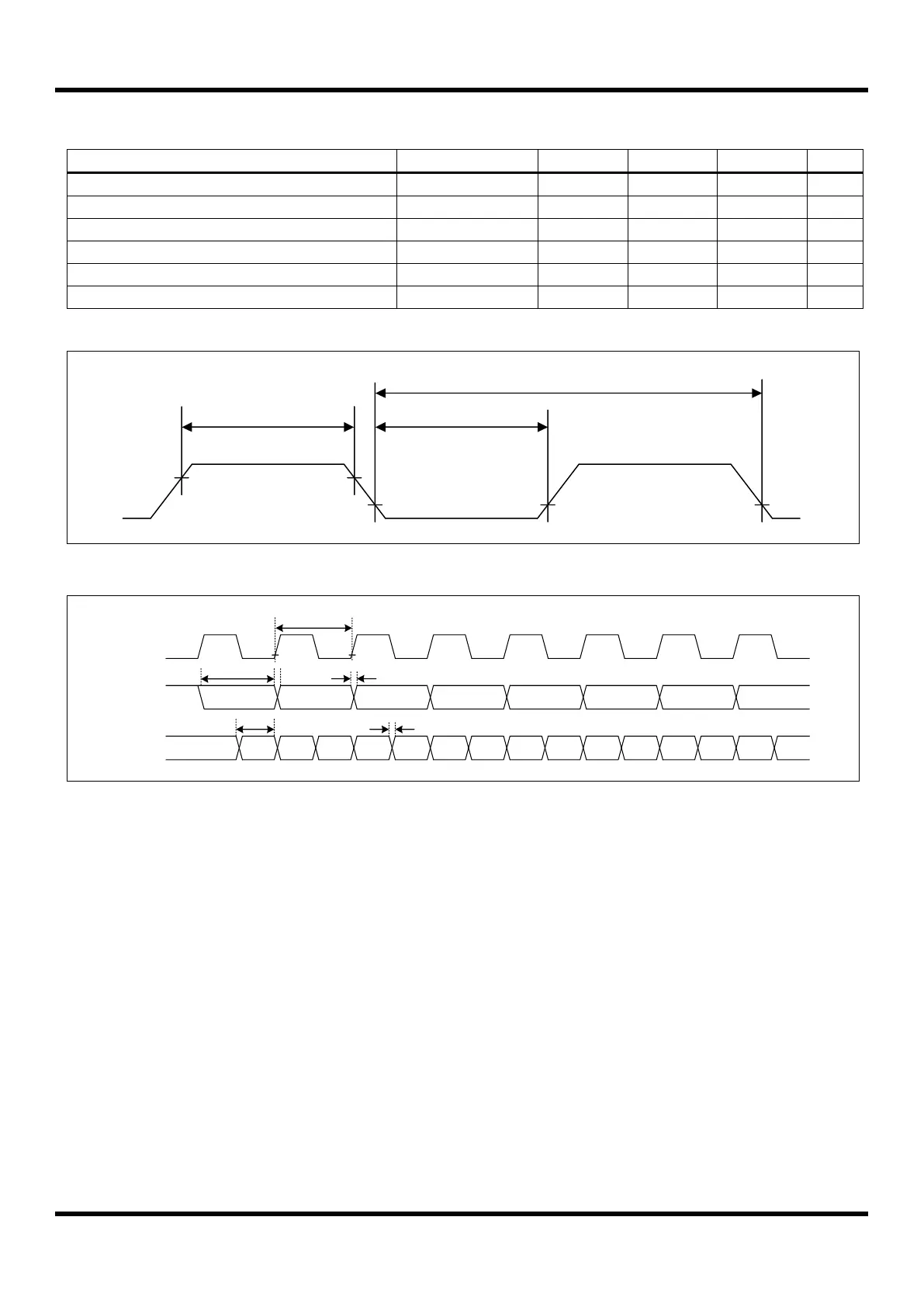

Figure 7.3 Waveform for UART0/1/2/3/4 Timing Characteristics

Shift Clock

Data Out D1 D2 D3 D4 D5 D6 D7D0

ValidData In Valid Valid Valid Valid Valid Valid Valid

tSCK

tS1

tH1

tH2

tS2

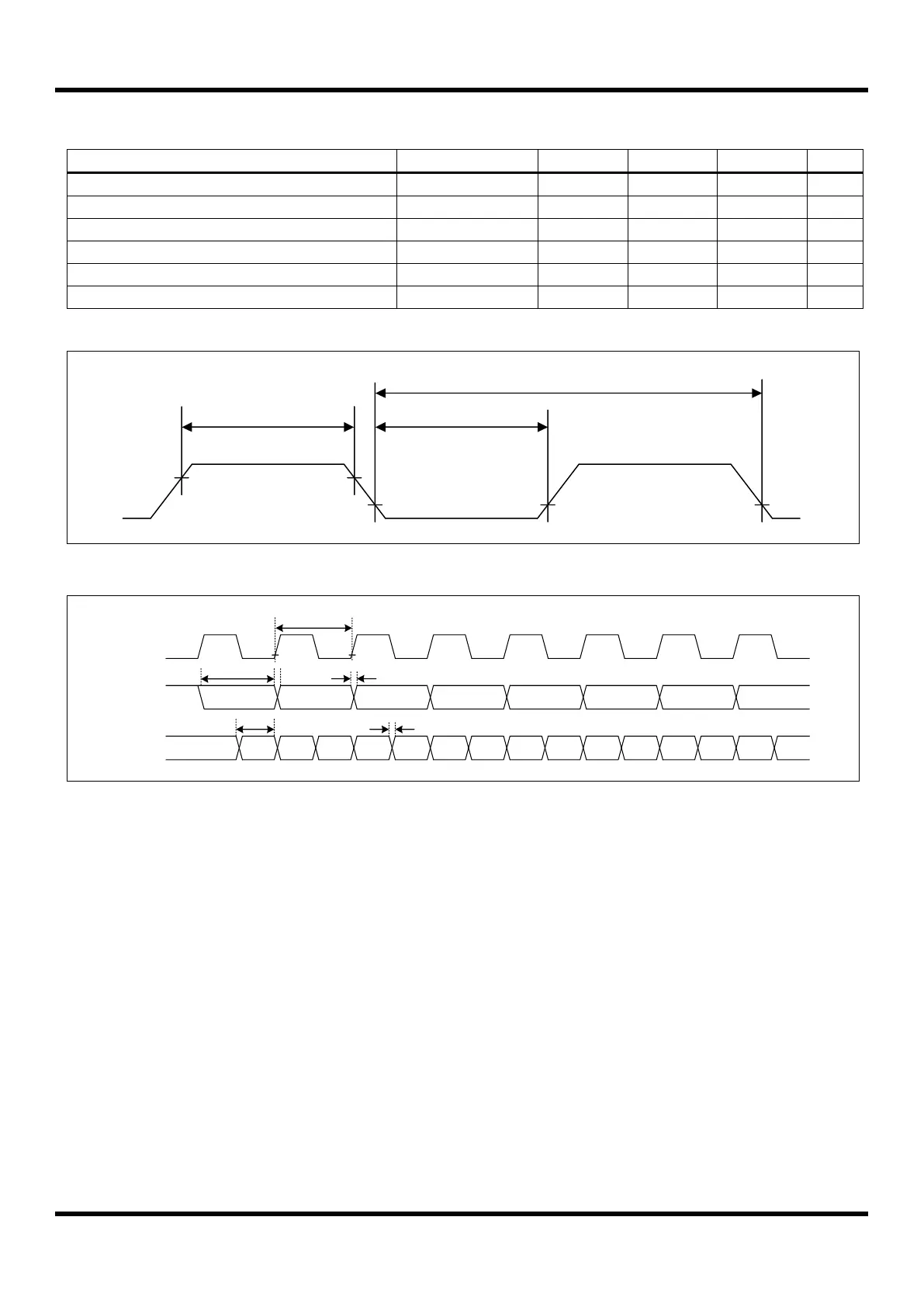

Figure 7.4 Timing Waveform for the UART0/1/2/3/4 Module

Loading...

Loading...