314

ABOV Semiconductor Co., Ltd.

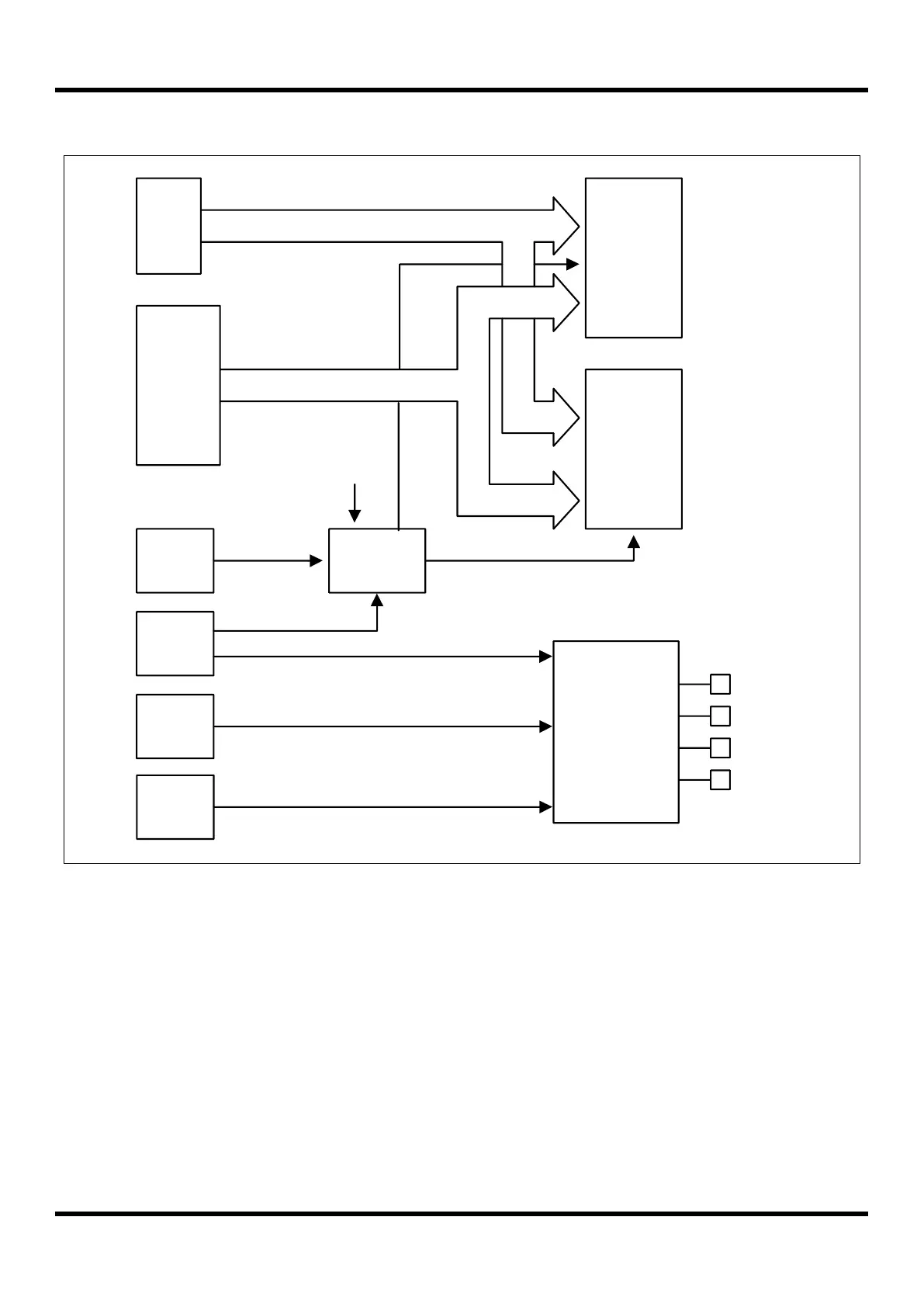

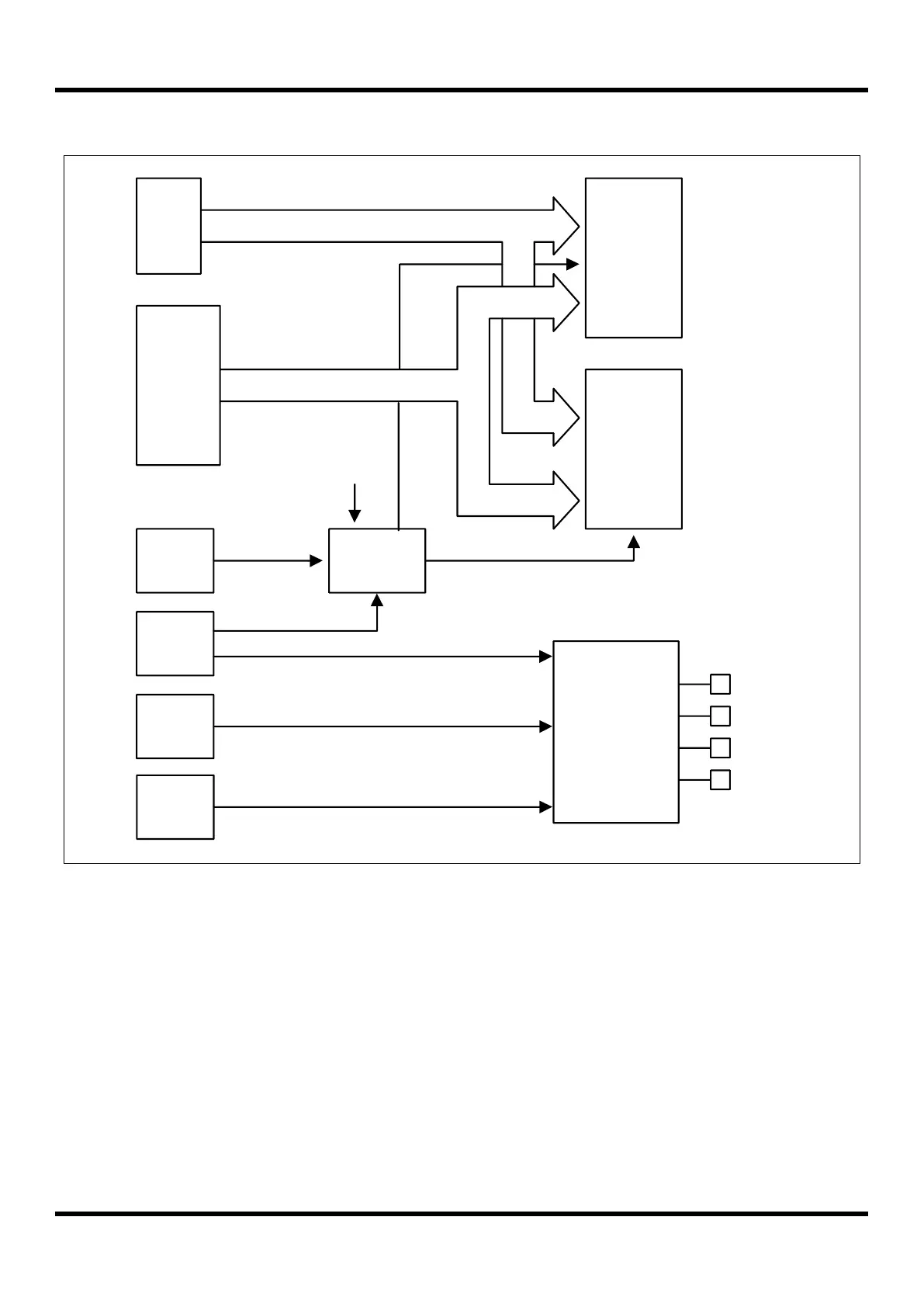

11.16.6 Block Diagram

Port

Latch

fLCD

LCD

Display

RAM

LCDCRL

LCDCRH

Timing

Controller

LCD

Voltage

Bias

COM/Port

Driver

VLC2

VLC1

VLC0

VLC3

LCDCCR

LCDBCR

SEG/Port

Driver

Figure 11.98 LCD Circuit Block Diagram

NOTE)

1. The clock and duty for LCD driver is automatically initialized by hardware, whenever LCDCRL

register data value is rewritten. So, don’t rewrite LCDCRL frequently

2. fLCD Clock Source is used f

WCK

(Watch Timer Clock).

Loading...

Loading...