Lesson 3 – Setting up the Digitizers in the Digital Clock Domain

207

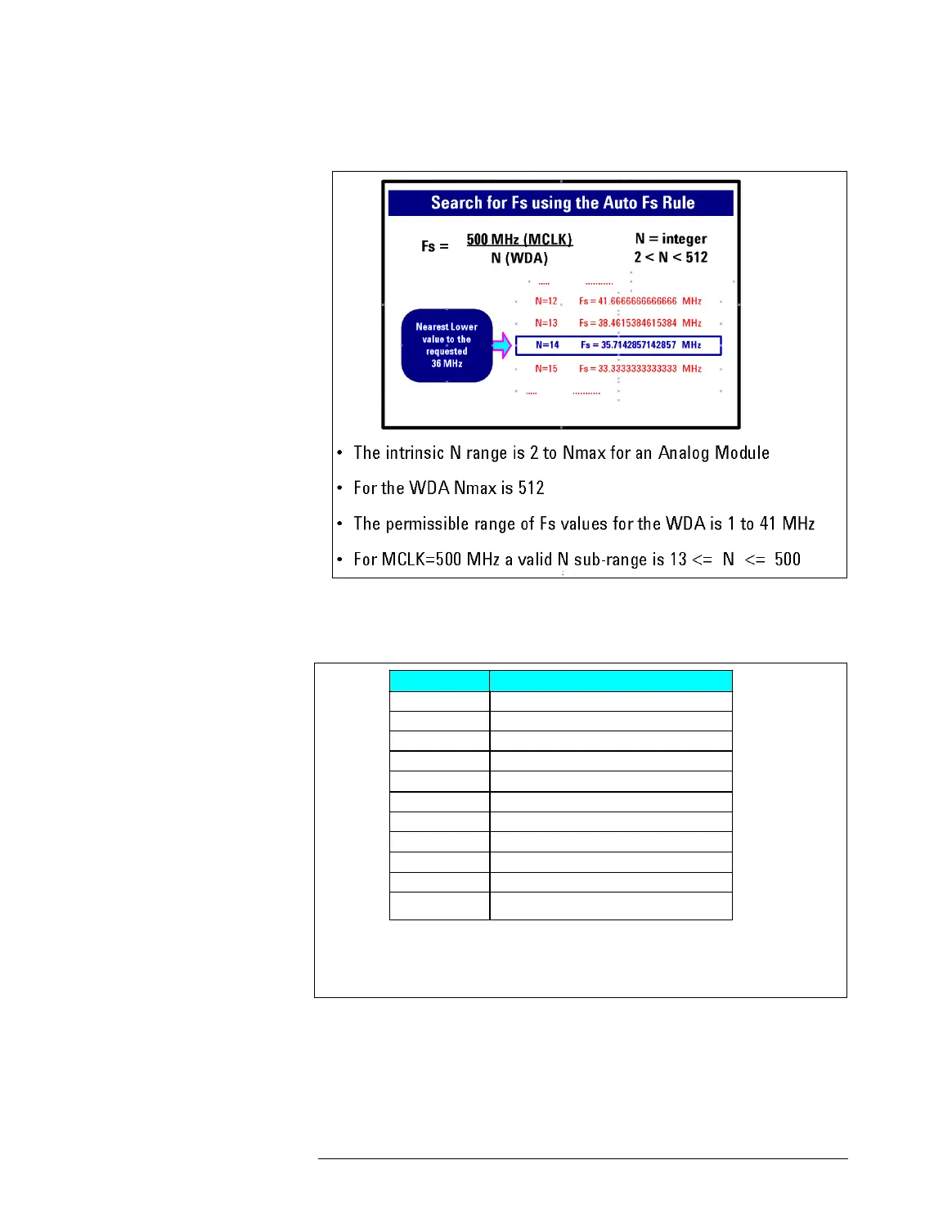

Calculation of Fs and N

These are the valid N values for all analog modules which divide

the master clock to generate the sampling frequency Fs.

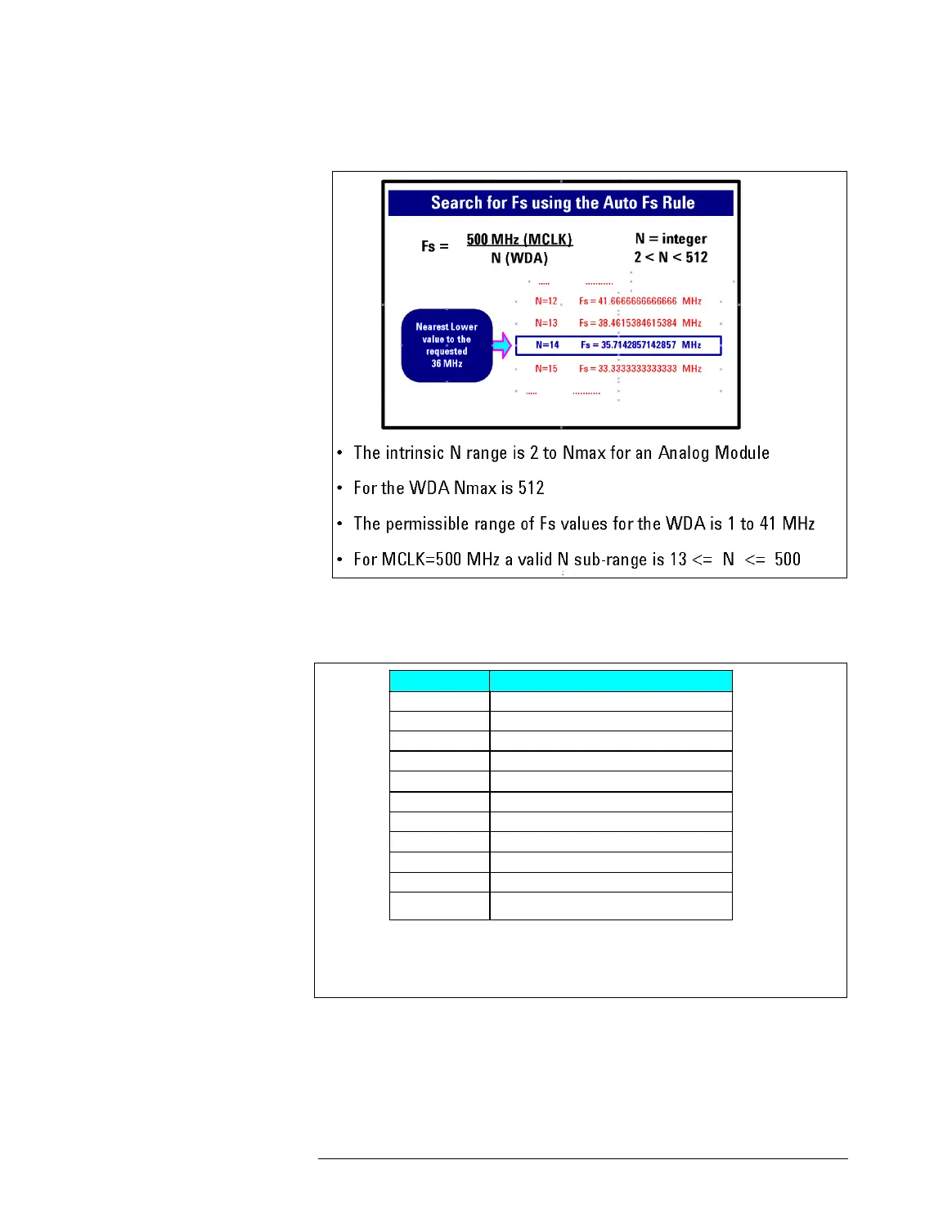

Valid Clock Divisors of Analog Modules

* The Nmin value applies for the minimum master clock frequency of 200MHz and the

Nmax value for the maximum frequency of 500 MHz. The equation Fs = MCLK/N must

always result in an Fs value in the module’s Fs range.

Analog Module Nmin - Nmax *

WDB 98 – 62500

WDE 40 - 4000

WDA 5 - 500

WDD 1 – 500 (4 – 500 for sampler mode)

SPA 200 - 62500

SPB 20 - 5000

WGA 196 - 62500

WGE 7 - 62500

WGB 2 - 62500

WGD 1 - 61440

WGF N must be set to -16, -8, -4, -2, 1, 2, 4 or 8.

(-16, -8, -4 and -2 mean 1/16, 1/8, 1/4 and 1/2)

Loading...

Loading...