110

8331B–AVR–03/12

Atmel AVR XMEGA AU

• Bit 7 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write

this bit to zero when this register is written.

• Bit 6 – USB: USB Module

Setting this bit stops the clock to the USB module. When this bit is cleared, the peripheral should

be reinitialized to ensure proper operation.

• Bit 5 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write

this bit to zero when this register is written.

• Bit 4 – AES: AES Module

Setting this bit stops the clock to the AES module. When this bit is cleared, the peripheral should

be reinitialized to ensure proper operation.

• Bit 3 – EBI: External Bus Interface

Setting this bit stops the clock to the external bus interface. When this bit is cleared, the periph-

eral should be reinitialized to ensure proper operation.

• Bit 2 – RTC: Real-Time Counter

Setting this bit stops the clock to the real-time counter. When this bit is cleared, the peripheral

should be reinitialized to ensure proper operation.

• Bit 1 – EVSYS: Event System

Setting this stops the clock to the event system. When this bit is cleared, the module will con-

tinue as before it was stopped.

• Bit 0 – DMA: DMA Controller

Setting this bit stops the clock to the DMA controller. This bit can be set only if the DMA control-

ler is disabled.

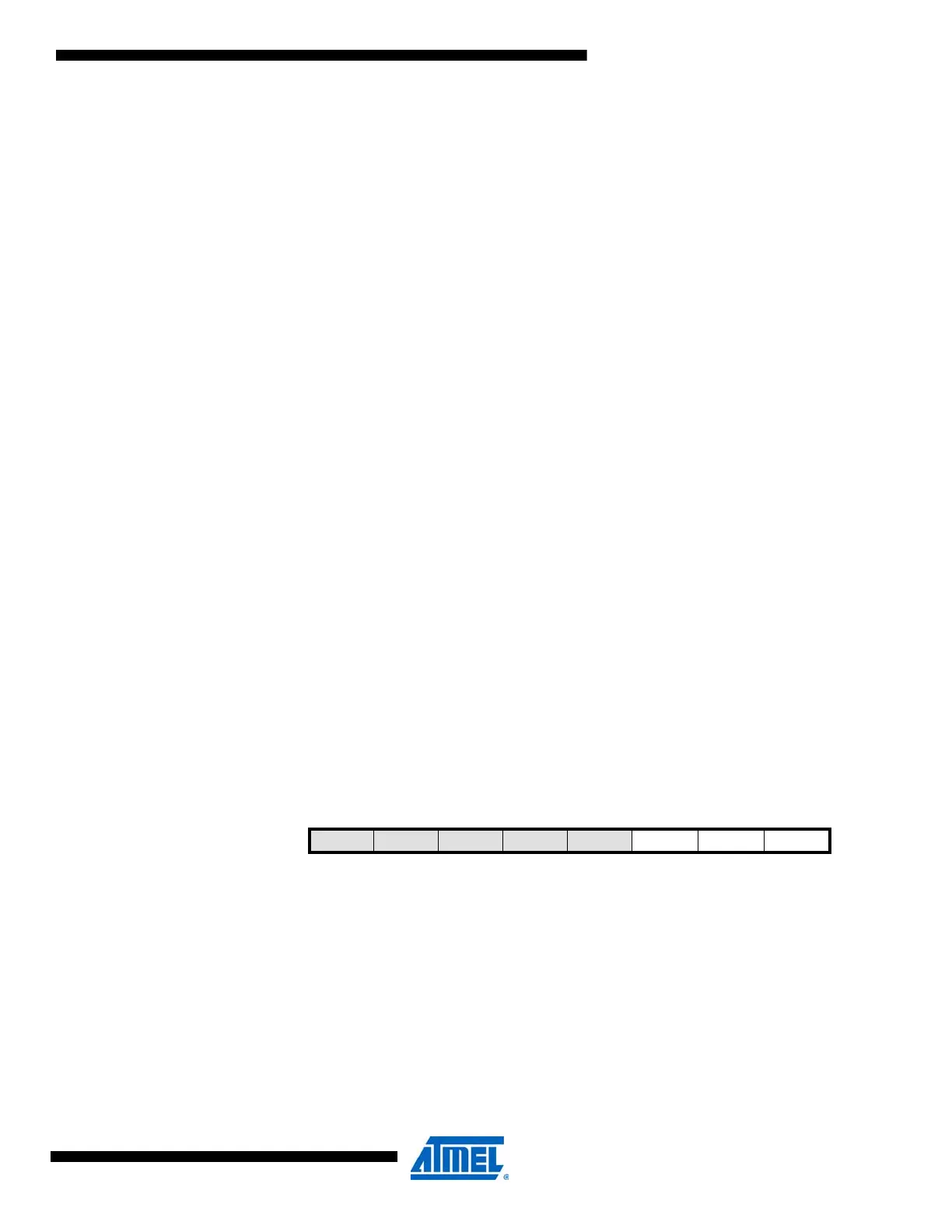

8.7.2 PRPA/B – Power Reduction Port A/B register

Note: Disabling of analog modules stops the clock to the analog blocks themselves and not only the

interfaces.

• Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 2 – DAC: Power Reduction DAC

Setting this bit stops the clock to the DAC. The DAC should be disabled before stopped.

Bit 765432 1 0

+0x01/+0x02 – – – – – DAC ADC AC PRPA/B

Read/WriteRRRRRR/WR/WR/W

Initial Value000000 0 0

Loading...

Loading...