213

8331B–AVR–03/12

Atmel AVR XMEGA AU

• Bit 7:5 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 4 – FDDBD: Fault Detection on Debug Break Detection

By default, when this bit is cleared and fault protection is enabled, and OCD break request is

treated as a fault. When this bit is set, an OCD break request will not trigger a fault condition.

• Bit 3 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write

this bit to zero when this register is written.

• Bit 2 – FDMODE: Fault Detection Restart Mode

This bit sets the fault protection restart mode. When this bit is cleared, latched mode is used,

and when it is set, cycle-by-cycle mode is used.

In latched mode, the waveform output will remain in the fault state until the fault condition is no

longer active and the FDF has been cleared by software. When both conditions are met, the

waveform output will return to normal operation at the next UPDATE condition.

In cycle-by-cycle mode, the waveform output will remain in the fault state until the fault condition

is no longer active. When this condition is met, the waveform output will return to normal opera-

tion at the next UPDATE condition

.

• Bit 1:0 – FDACT[1:0]: Fault Detection Action

These bits define the action performed, according to Table 16-1, when a fault condition is

detected.

16.7.4 STATUS – Status register

• Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

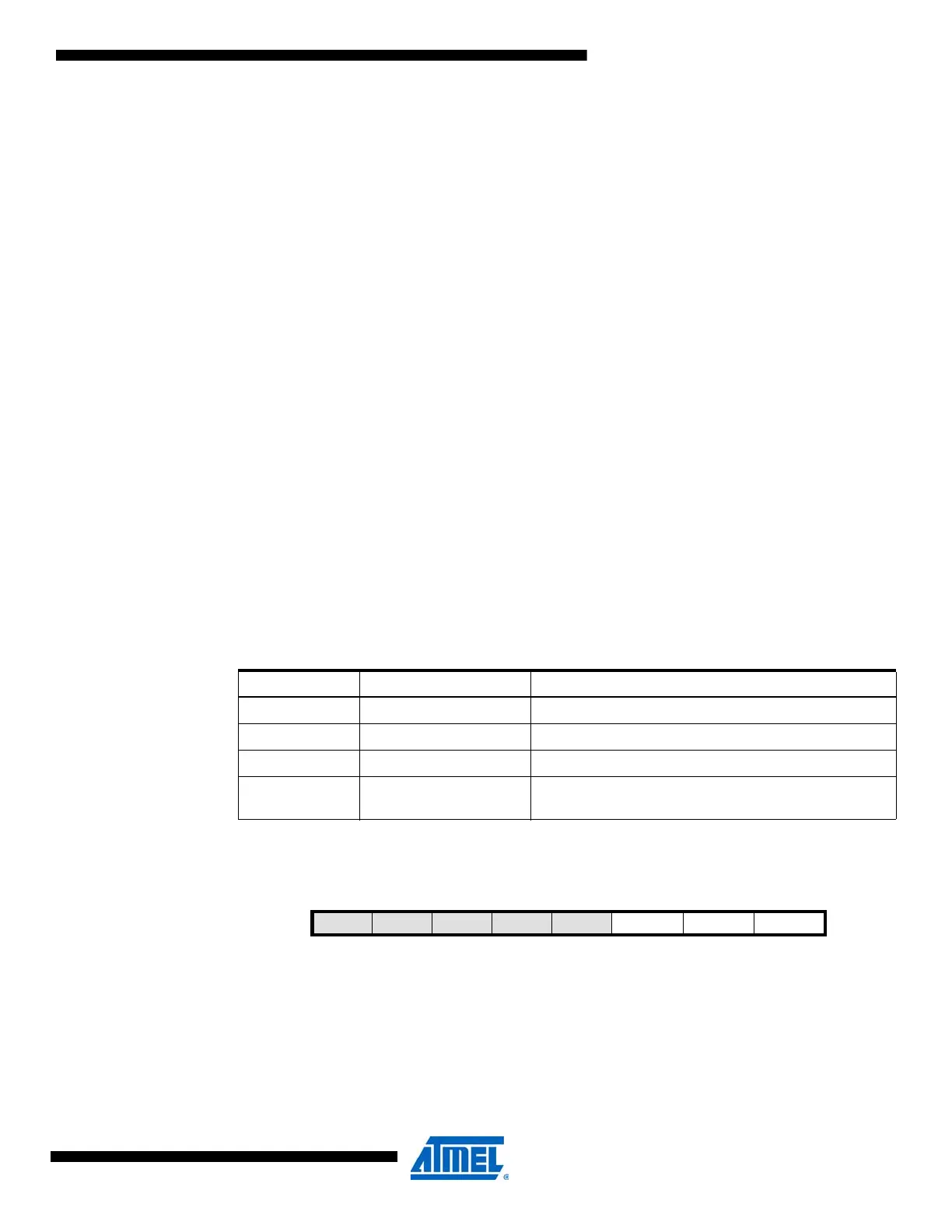

Table 16-1. Fault actions

FDACT[1:0] Group Configuration Description

00 NONE None (fault protection disabled)

01 Reserved

10 Reserved

11 CLEARDIR Clear all direction (DIR) bits which correspond to the

enabled DTI channel(s); i.e., tri-state the outputs

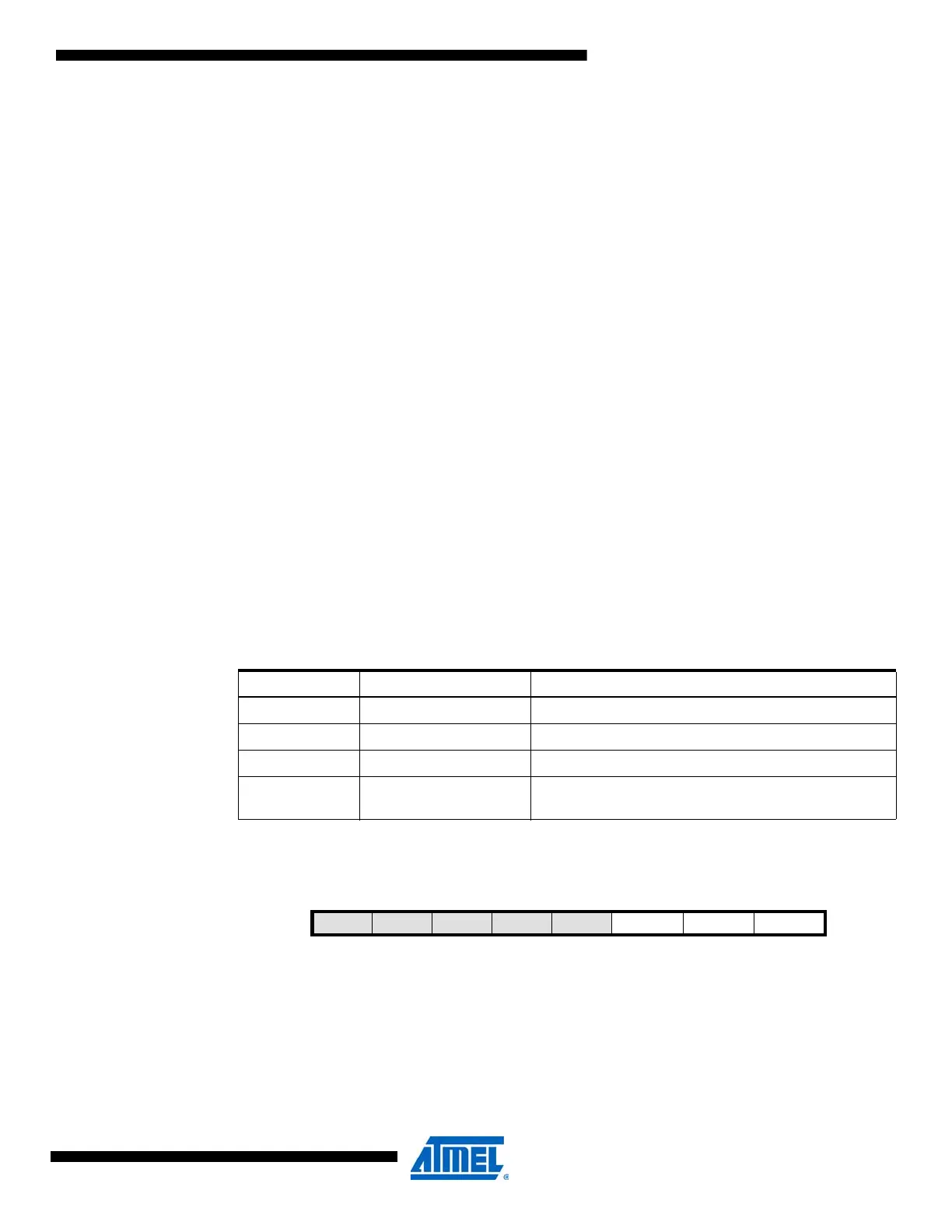

Bit 76543 2 1 0

+0x04 – – – – – FDF DTHSBUFV DTLSBUFV STATUS

Read/Write R R R R R R/W R/W R/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...