224

8331B–AVR–03/12

Atmel AVR XMEGA AU

• Bit 7:0 – CNT[7:0]: Counter Value Low

These bits hold the LSB of the 16-bit real-time counter value.

18.3.7 CNTH – Counter Register High

• Bit 7:0 – CNT[15:8]: Counter Value High

These bits hold the MSB of the 16-bit real-time counter value.

18.3.8 PERL – Period Register Low

The PERH and PERL register pair represents the 16-bit value, PER. PER is constantly com-

pared with the counter value (CNT). A match will set OVFIF in the INTFLAGS register and clear

CNT. Reading and writing 16-bit values requires special attention. Refer to ”Accessing 16-bit

Registers” on page 13 for details.

Due to synchronization between the RTC clock and system clock domains, there is a latency of

two RTC clock cycles from updating the register until this has an effect. Application software

needs to check that the SYNCBUSY flag in the ”STATUS – Status register” on page 222 is

cleared before writing to this register.

• Bit 7:0 – PER[7:0]: Period Low

These bits hold the LSB of the 16-bit RTC TOP value.

18.3.9 PERH – Period Register High

• Bits 7:0 – PER[15:8]: Period High

These bits hold the MSB of the 16-bit RTC TOP value.

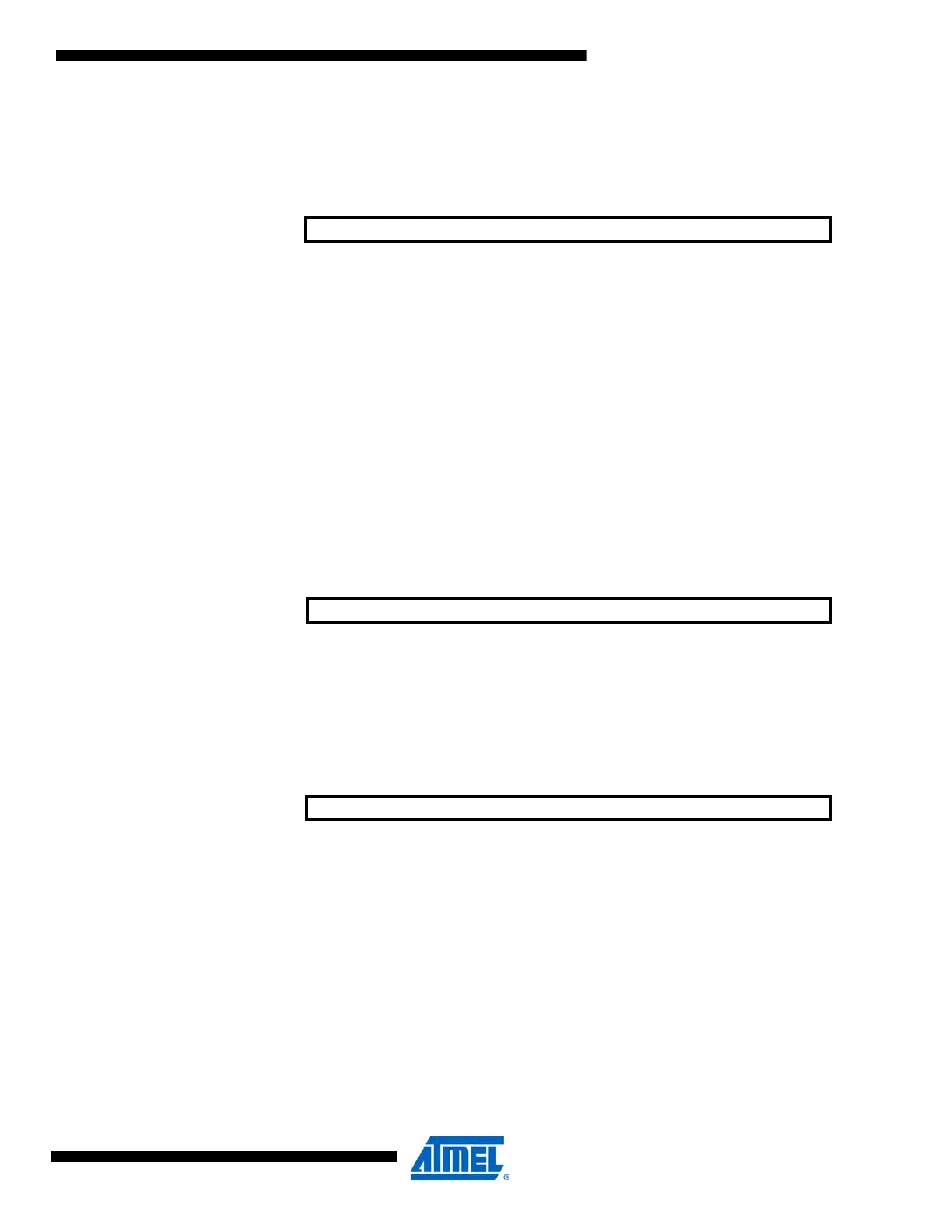

Bit 76543210

+0x09 CNT[15:8] CNTH

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

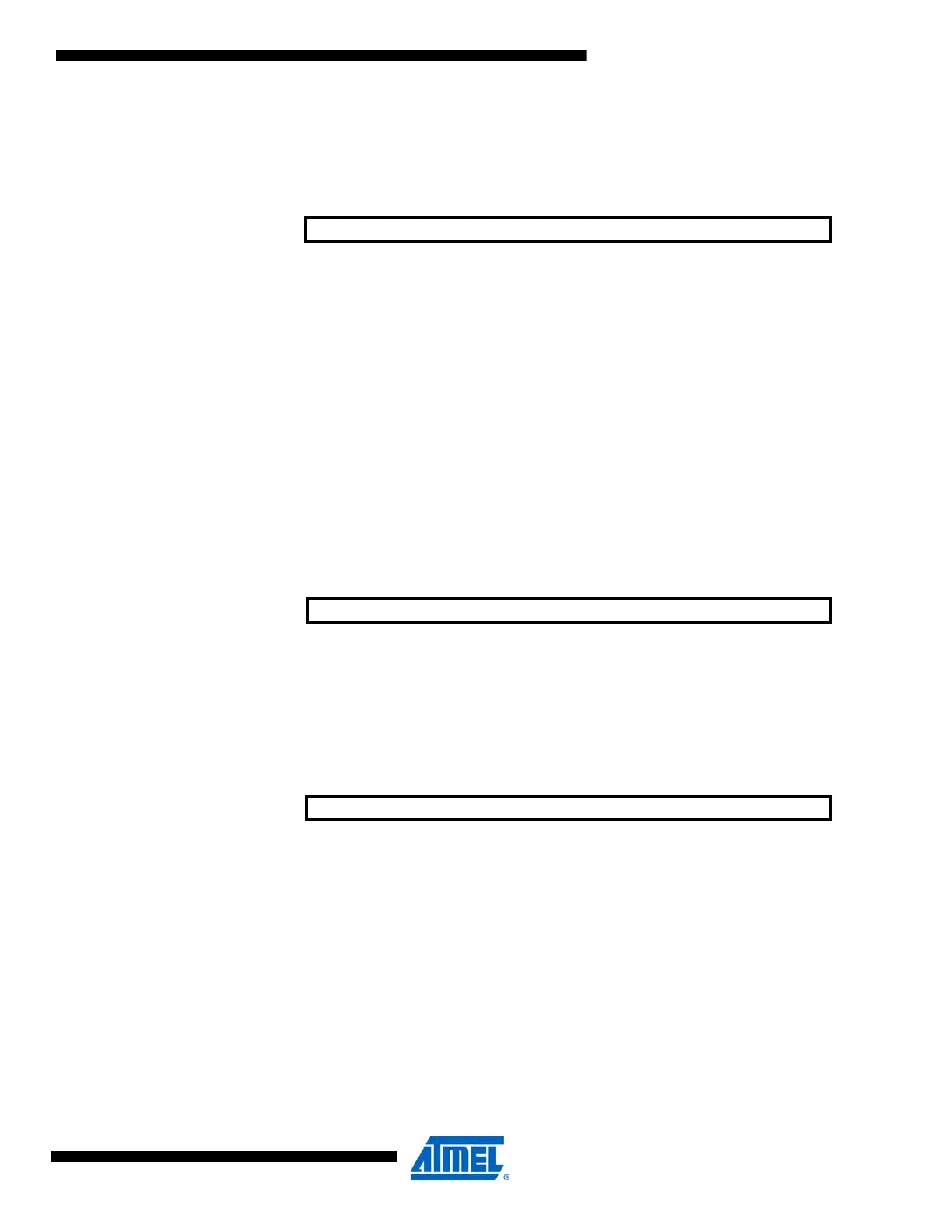

Bit 76543210

+0x0A PER[7:0] PERL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value 1 1 1 1 1 1 1 1

Bit 76543210

+0x0B PER[15:8] PERH

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value11111111

Loading...

Loading...