267

8331B–AVR–03/12

Atmel AVR XMEGA AU

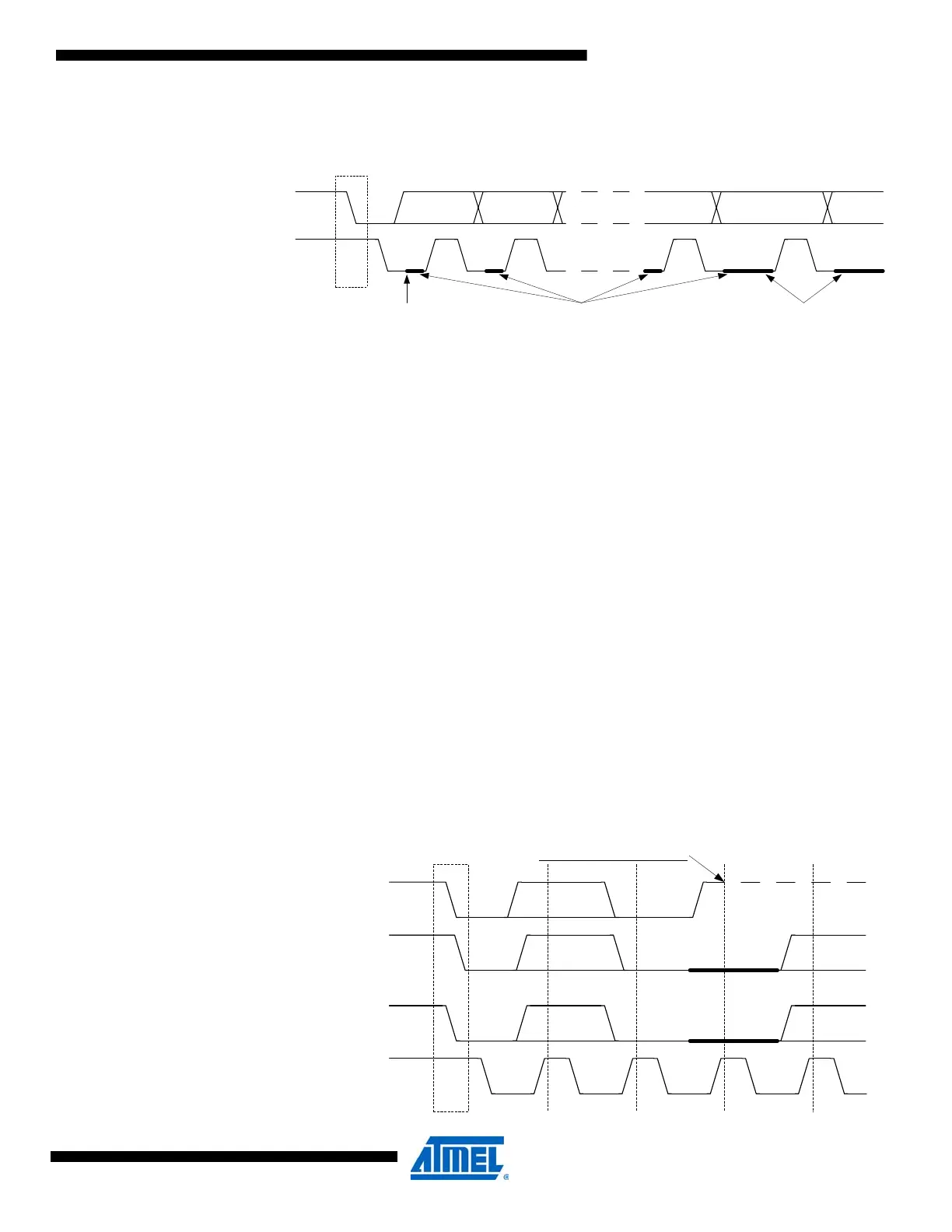

Three types of clock stretching can be defined, as shown in Figure 21-8.

Figure 21-8. Clock stretching

(1)

.

Note: 1. Clock stretching is not supported by all I

2

C slaves and masters.

If a slave device is in sleep mode and a START condition is detected, the clock stretching nor-

mally works during the wake-up period. For AVR XMEGA devices, the clock stretching will be

either directly before or after the ACK/NACK bit, as AVR XMEGA devices do not need to wake

up for transactions that are not addressed to it.

A slave device can slow down the bus frequency by stretching the clock periodically on a bit

level. This allows the slave to run at a lower system clock frequency. However, the overall per-

formance of the bus will be reduced accordingly. Both the master and slave device can

randomly stretch the clock on a byte level basis before and after the ACK/NACK bit. This pro-

vides time to process incoming or prepare outgoing data, or perform other time-critical tasks.

In the case where the slave is stretching the clock, the master will be forced into a wait state until

the slave is ready, and vice versa.

21.3.8 Arbitration

A master can start a bus transaction only if it has detected that the bus is idle. As the TWI bus is

a multi-master bus, it is possible that two devices may initiate a transaction at the same time.

This results in multiple masters owning the bus simultaneously. This is solved using an arbitra-

tion scheme where the master loses control of the bus if it is not able to transmit a high level on

the SDA line. The masters who lose arbitration must then wait until the bus becomes idle (i.e.,

wait for a STOP condition) before attempting to reacquire bus ownership. Slave devices are not

involved in the arbitration procedure.

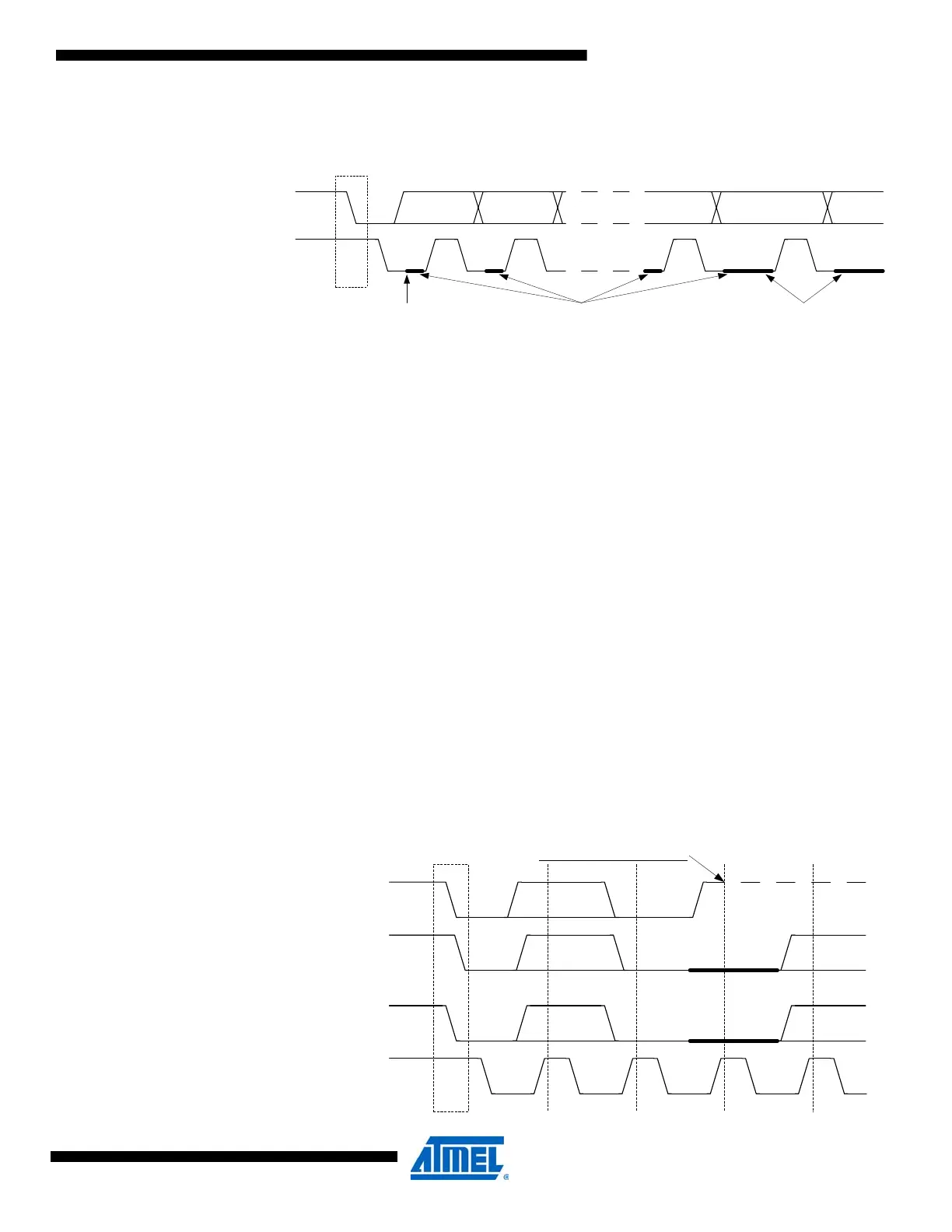

Figure 21-9. TWI arbitration.

SDA

SCL

S

ACK/NACKbit 0bit 7 bit 6

Periodic clock

stretching

Random clock

stretching

Wakeup clock

stretching

DEVICE1_SDA

SDA

(wired-AND)

DEVICE2_SDA

SCL

S

bit 7 bit 6 bit 5 bit 4

DEVICE1 Loses arbitration

Loading...

Loading...