266

8331B–AVR–03/12

Atmel AVR XMEGA AU

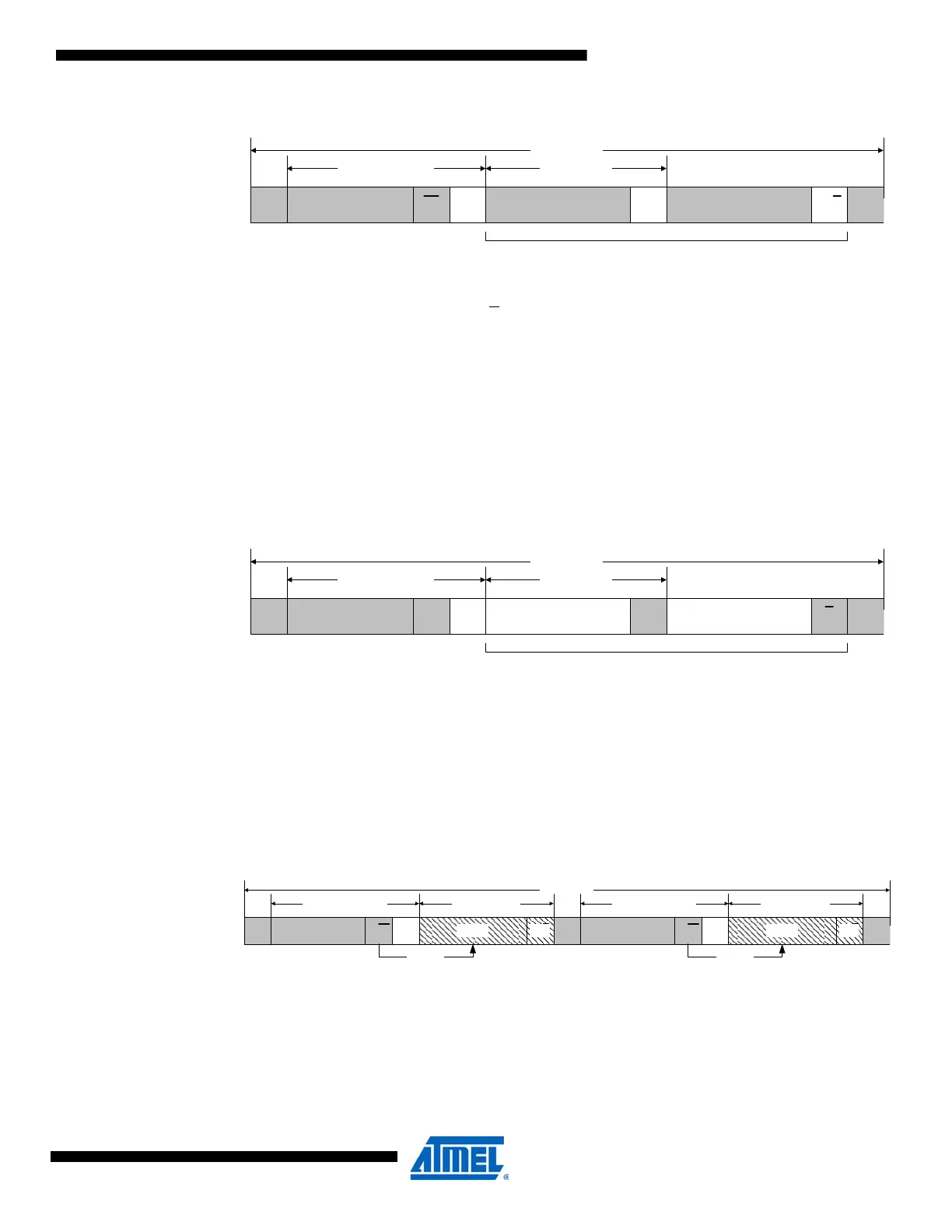

Figure 21-5. Master write transaction.

Assuming the slave acknowledges the address, the master can start transmitting data (DATA)

and the slave will ACK or NACK (A/A

) each byte. If no data packets are to be transmitted, the

master terminates the transaction by issuing a STOP condition (P) directly after the address

packet. There are no limitations to the number of data packets that can be transferred. If the

slave signals a NACK to the data, the master must assume that the slave cannot receive any

more data and terminate the transaction.

Figure 21-6 on page 266 illustrates the master read transaction. The master initiates the trans-

action by issuing a START condition followed by an address packet with the direction bit set to

one (ADDRESS+R). The addressed slave must acknowledge the address for the master to be

allowed to continue the transaction.

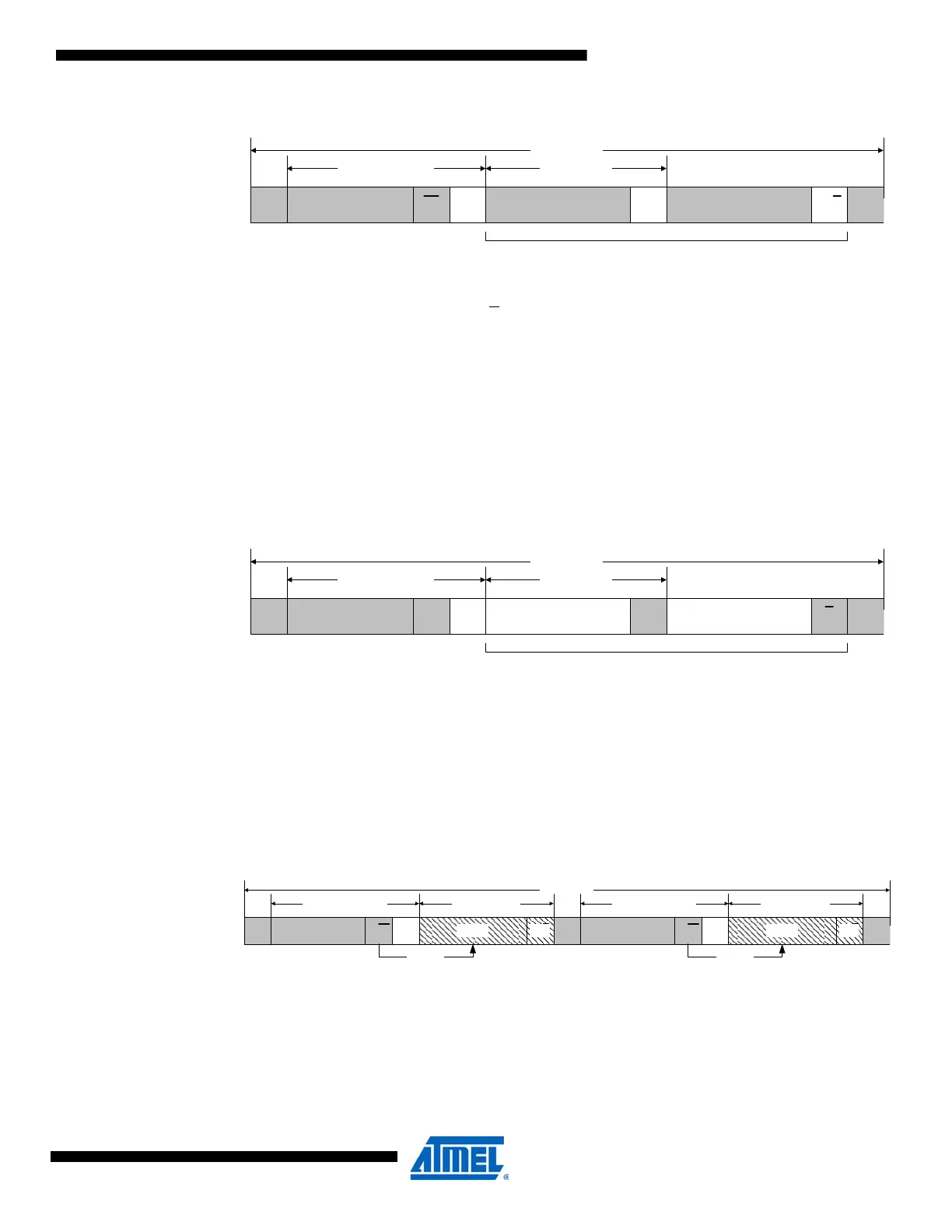

Figure 21-6. Master read transaction.

Assuming the slave acknowledges the address, the master can start receiving data from the

slave. There are no limitations to the number of data packets that can be transferred. The slave

transmits the data while the master signals ACK or NACK after each data byte. The master ter-

minates the transfer with a NACK before issuing a STOP condition.

Figure 21-7 illustrates a combined transaction. A combined transaction consists of several read

and write transactions separated by repeated START conditions (Sr).

Figure 21-7. Combined Transaction.

21.3.7 Clock and Clock Stretching

All devices connected to the bus are allowed to stretch the low period of the clock to slow down

the overall clock frequency or to insert wait states while processing data. A device that needs to

stretch the clock can do this by holding/forcing the SCL line low after it detects a low level on the

line.

S A A A/A PWADDRESS DATA DATA

Address Packet Data Packet

Transaction

N data packets

S

R

A A AADDRESS DATA DATA P

Transaction

Address Packet Data Packet

N data packets

S A SrA/AR/W DATA A/A

P

ADDRESS DATA R/WADDRESS

Transaction

Address Packet #1 N Data Packets M Data Packets

Address Packet #2

Direction

Direction

A

Loading...

Loading...