278

8331B–AVR–03/12

Atmel AVR XMEGA AU

•Bit 5 – CLKHOLD: Clock Hold

This flag is set when the master is holding the SCL line low. This is a status flag and a read-only

flag that is set when RIF or WIF is set. Clearing the interrupt flags and releasing the SCL line will

indirectly clear this flag.

The flag is also cleared automatically for the same conditions as RIF.

•Bit 4

– RXACK: Received Acknowledge

This flag contains the most recently received acknowledge bit from the slave. This is a read-only

flag. When read as zero, the most recent acknowledge bit from the slave was ACK, and when

read as one the most recent acknowledge bit was NACK.

•Bit 3

– ARBLOST: Arbitration Lost

This flag is set if arbitration is lost while transmitting a high data bit or a NACK bit, or while issu-

ing a START or repeated START condition on the bus. Writing a one to this bit location will clear

ARBLOST.

Writing the ADDR register will automatically clear ARBLOST.

•Bit 2

– BUSERR: Bus Error

This flag is set if an illegal bus condition has occurred. An illegal bus condition occurs if a

repeated START or a STOP condition is detected, and the number of received or transmitted

bits from the previous START condition is not a multiple of nine. Writing a one to this bit location

will clear BUSERR.

Writing the ADDR register will automatically clear BUSERR.

• Bit 1:0

– BUSSTATE[1:0]: Bus State

These bits indicate the current TWI bus state as defined in Table 21-6. The change of bus state

is dependent on bus activity. Refer to the Section 21.4 ”TWI Bus State Logic” on page 268.

Writing 01 to the BUSSTATE bits forces the bus state logic into the idle state. The bus state logic

cannot be forced into any other state. When the master is disabled, and after reset, the bus state

logic is disabled and the bus state is unknown.

21.9.5 BAUD

– Baud Rate register

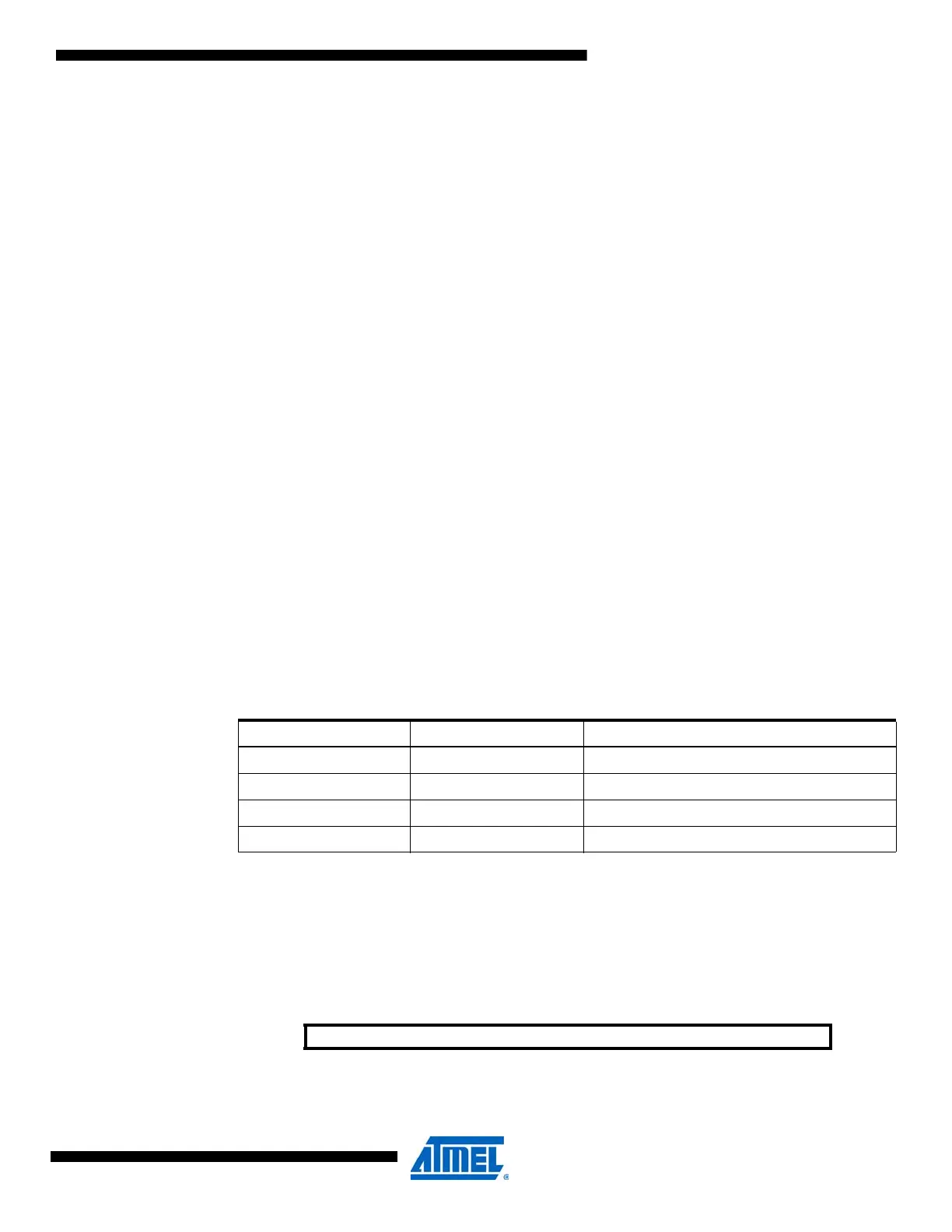

Table 21-6. TWI master bus state.

BUSSTATE[1:0] Group Configuration Description

00 UNKNOWN Unknown bus state

01 IDLE Idle bus state

10 OWNER Owner bus state

11 BUSY Busy bus state

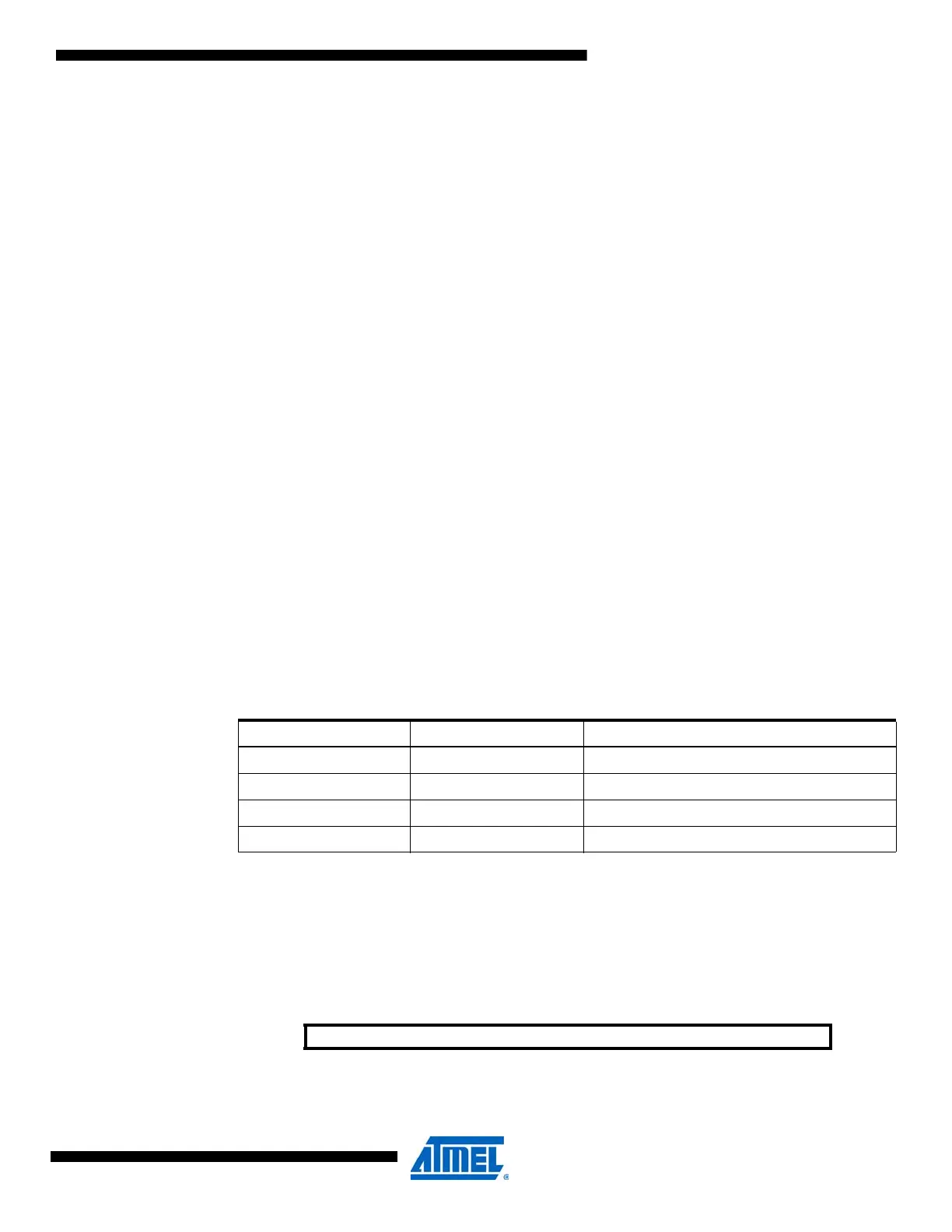

Bit 76543210

+0x04 BAUD[7:0] BAUD

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

Loading...

Loading...