326

8331B–AVR–03/12

Atmel AVR XMEGA AU

25.5.4 KEY – Key register

The KEY register is used to access the key memory. Before encryption/decryption can take

place, the key memory must be written sequentially, byte-by-byte, through the KEY register.

After encryption/decryption is done, the last subkey can be read sequentially, byte-by-byte,

through the KEY register.

Loading the initial data to the KEY register should be done after setting the appropriate AES

mode and direction.

25.5.5 INTCTRL

– Interrupt Control register

• Bit 7:2

– Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 1:0

– INTLVL[1:0]: Interrupt priority and enable

These bits enable the AES interrupt and select the interrupt level, as described in ”Interrupts and

Programmable Multilevel Interrupt Controller” on page 134. The enabled interrupt will be trig-

gered when the SRIF in the STATUS register is set.

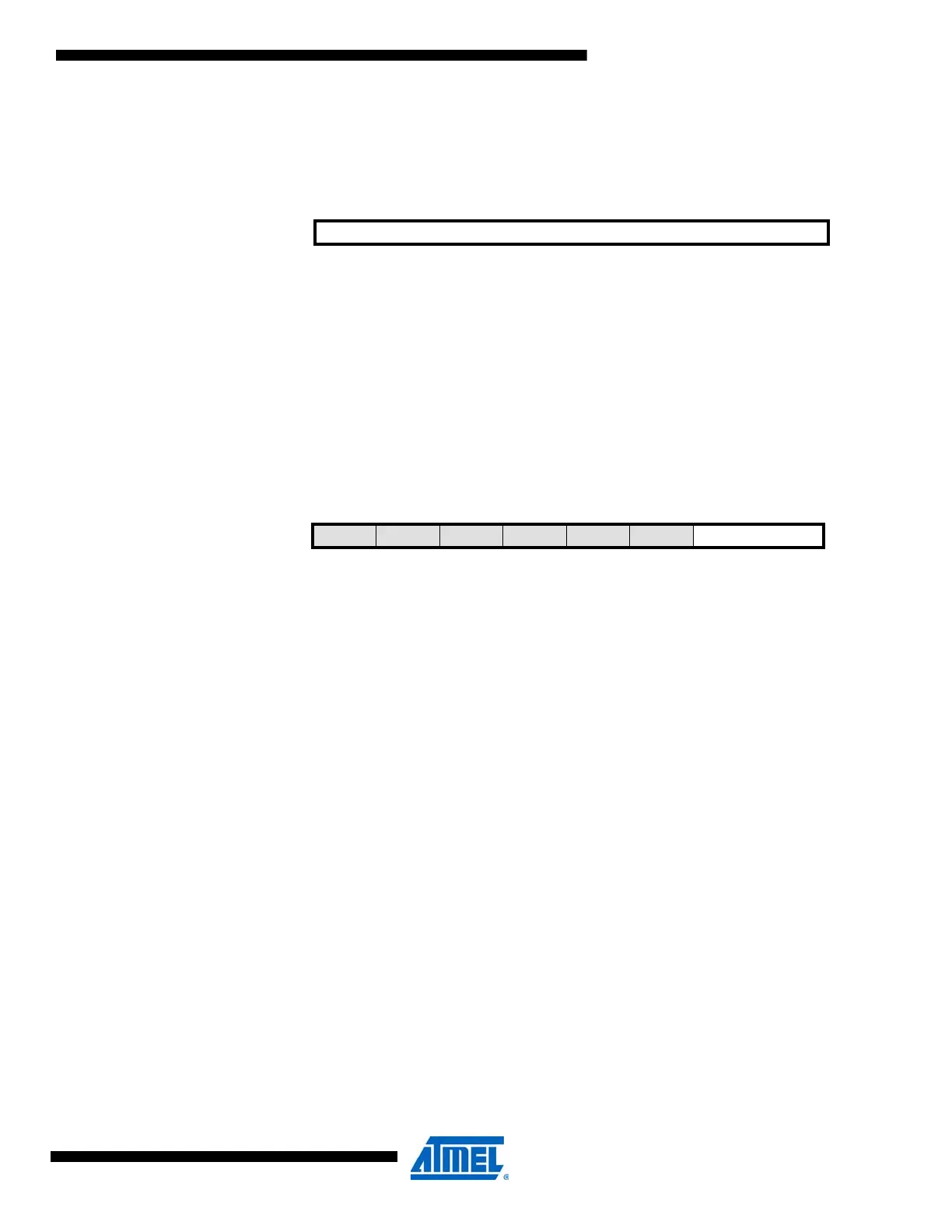

Bit 76543210

+0x03 KEY[7:0] KEY

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

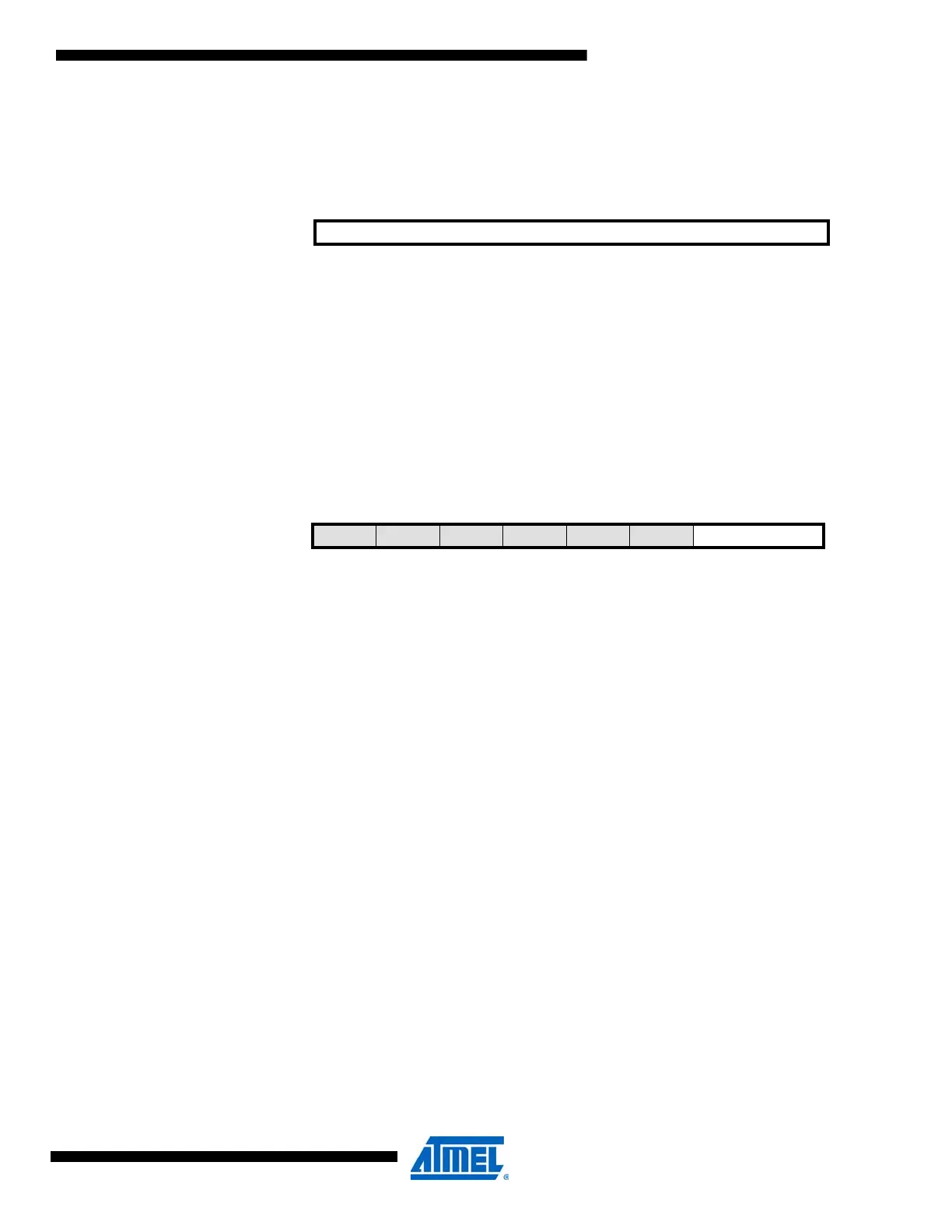

Bit 7654321 0

+0x04 – – – – – – INTLVL[1:0] INTCTRL

Read/WriteRRRRRRR/WR/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...