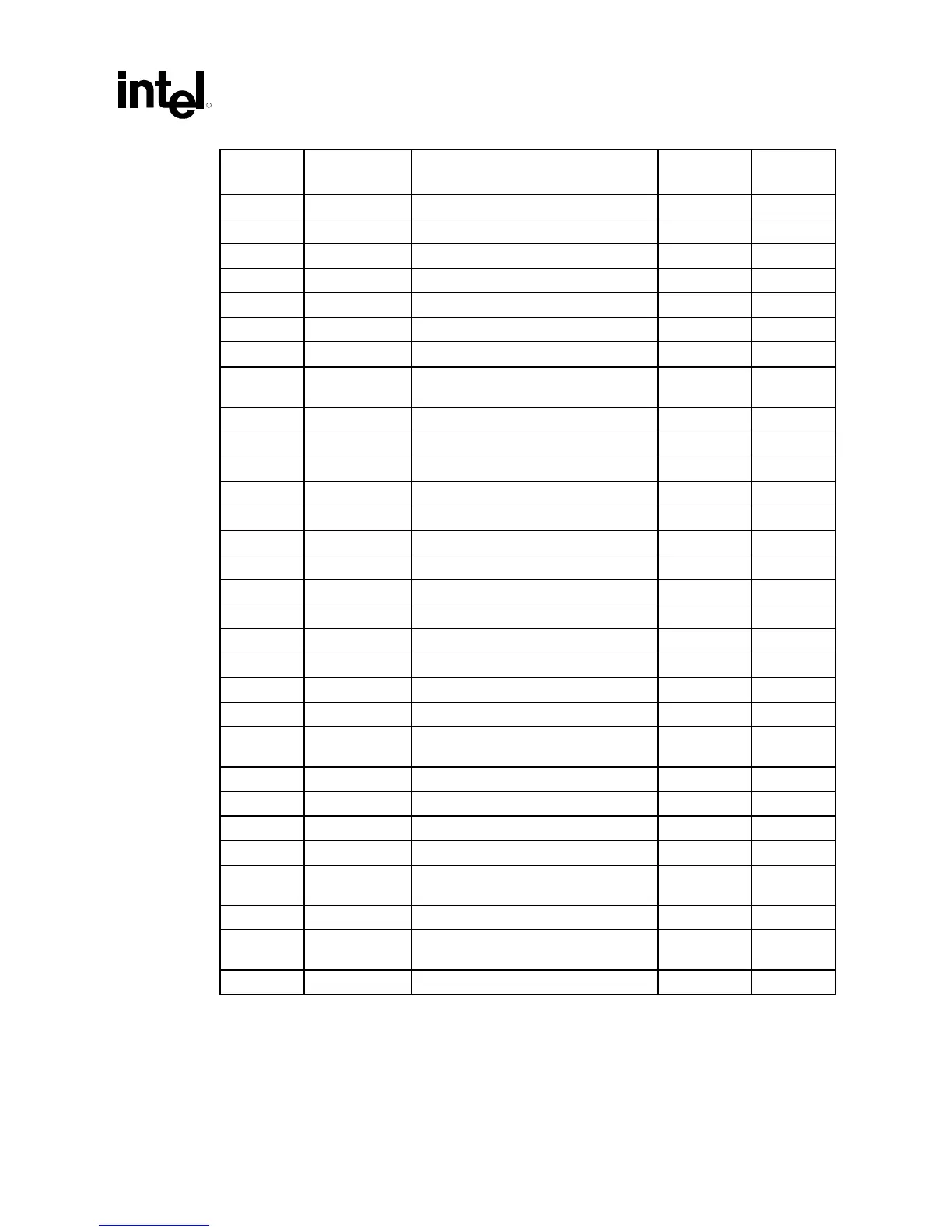

Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

Intel

®

82925X/82925XE MCH Datasheet 111

Address

Offset

Register

Symbol

Register Name

Default

Value

Access

BA–BBh SLOTSTS Slot Status 0X00h RO, R/W/C

BC–BDh RCTL Root Control 0000h R/W

BE–BFh — Reserved — —

C0–C3h RSTS Root Status 00000000h RO, R/W/C

C4–EBh — Reserved — —

EC–EFh PEGLC PCI Express*-Graphics Legacy Control 00000000h R/W, RO

F0–FFh — Reserved — —

100–103h VCECH Virtual Channel Enhanced Capability

Header

14010002h RO

104–107h PVCCAP1 Port VC Capability Register 1 00000001h RO, R/WO

108–10Bh PVCCAP2 Port VC Capability Register 2 00000001h RO

10C–10Dh PVCCTL Port VC Control 0000h R/W

10E–10Fh — Reserved — —

110–113h VC0RCAP VC0 Resource Capability 00000000h RO

114–117h VC0RCTL VC0 Resource Control 8000007Fh RO, R/W

118–119h — Reserved — —

11A–11Bh VC0RSTS VC0 Resource Status 0000h RO

11C–11Fh VC1RCAP VC1 Resource Capability 00008000h RO

120–123h VC1RCTL VC1 Resource Control 01000000h RO, R/W

124–125h — Reserved — —

126–127h VC1RSTS VC1 Resource Status 0000h RO

128–13Fh — Reserved — —

140–143h RCLDECH Root Complex Link Declaration

Enhanced Capability Header

00010005h RO

144–147h ESD Element Self Description 02000100h RO, R/WO

148–14Fh — Reserved — —

150–153h LE1D Link Entry 1 Description 00000000h RO, R/WO

154–157h — Reserved — —

158–15Fh LE1A Link Entry 1 Address 0000000000

000000h

R/WO

160–217h — Reserved — —

218–21Fh PEGSSTS PCI Express*-Graphics Sequence Status 0000000000

000FFFh

RO

220–FFFh — Reserved — —

Loading...

Loading...