Signal Description

R

Intel

®

82925X/82925XE MCH Datasheet 31

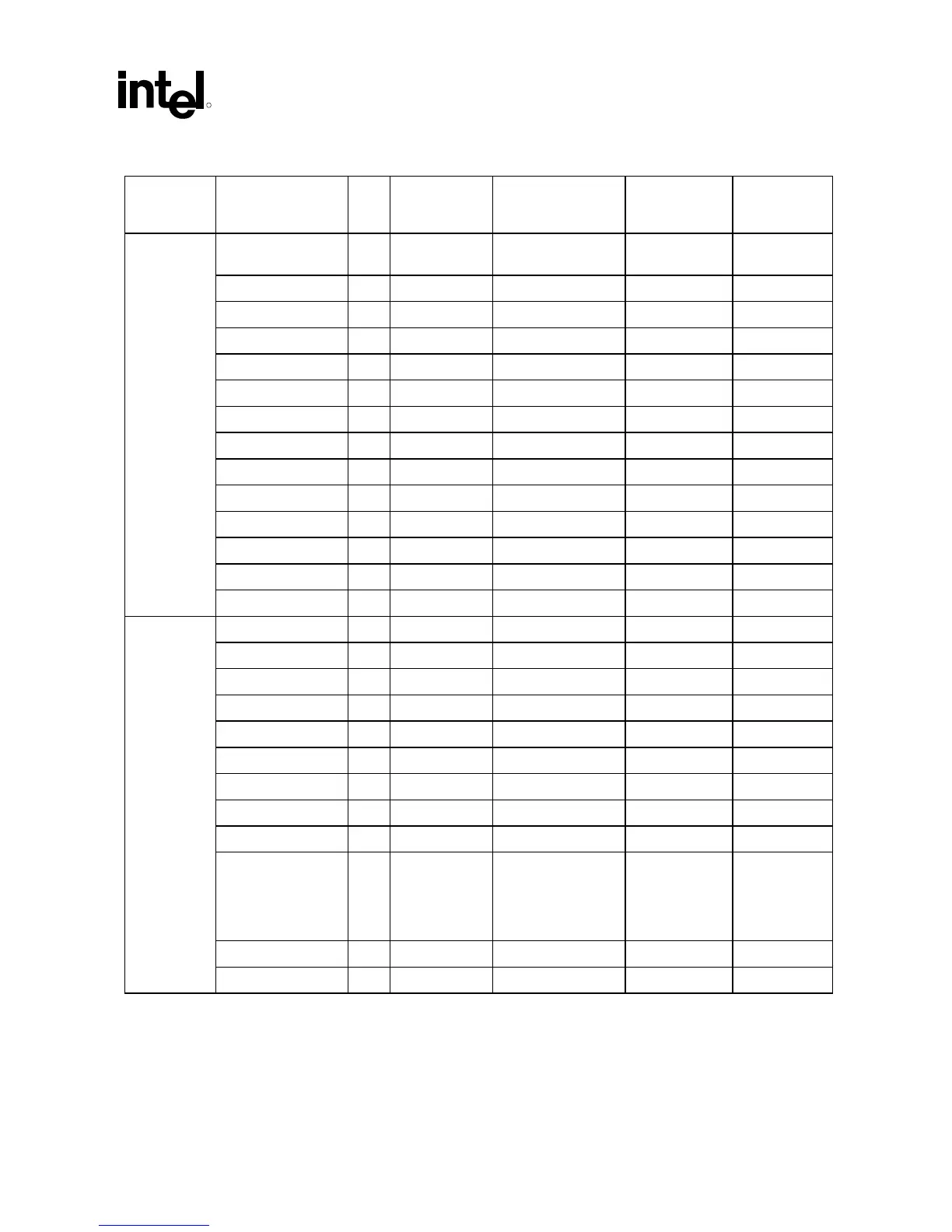

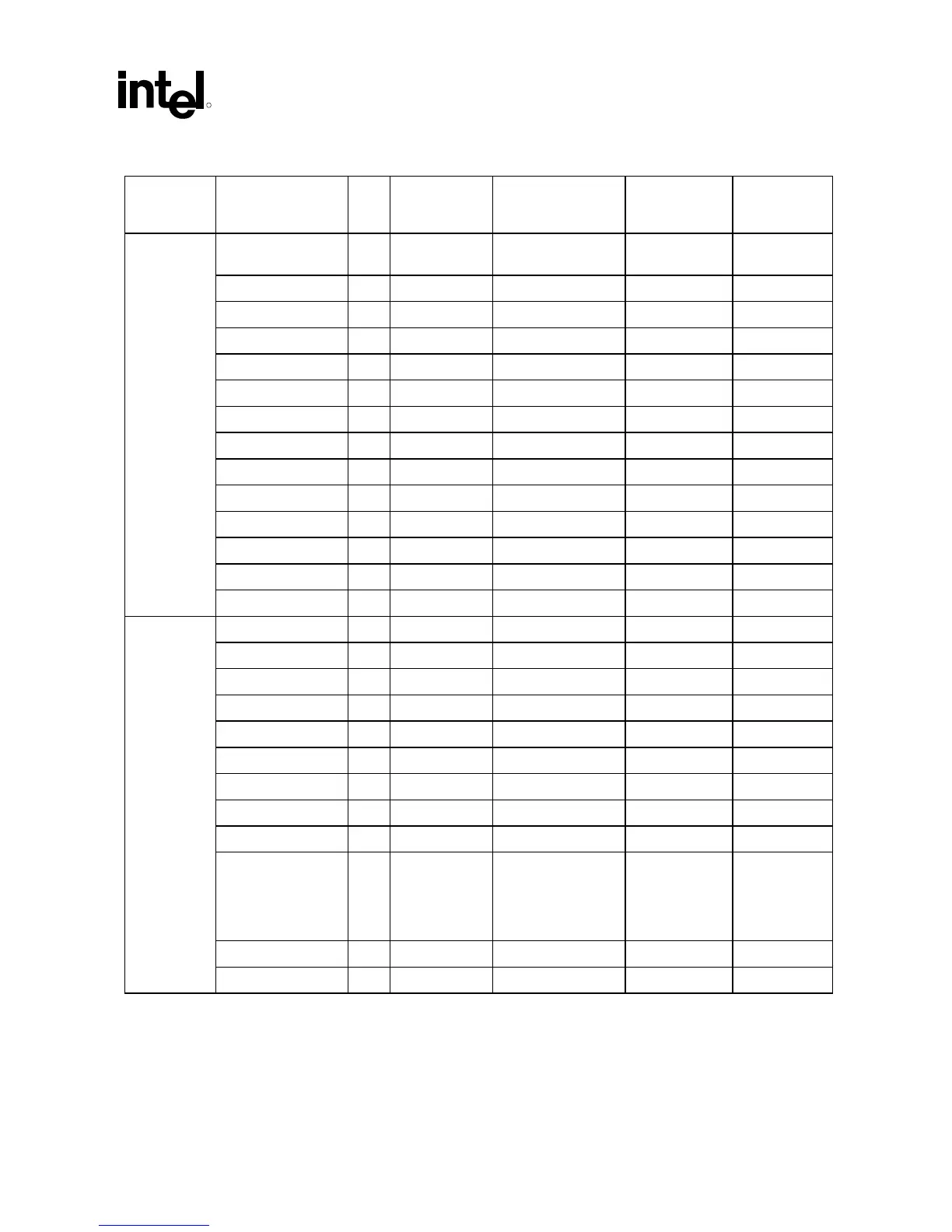

Table 2-1. Host Interface Reset and S3 States

Interface Signal Name I/O

State During

RSTIN#

Assertion

State After

RSTIN# De-

assertion

S3

Pull-up/

Pull-down

Host I/F HCPURST# O DRIVE LV TERM HV after

approximately 1ms

TRI (No VTT)

HADSTB[1:0]# I/O TERM HV TERM HV TRI (No VTT)

HA[31:3]# I/O TERM HV TERM HV TRI (No VTT)

HD[63:0] I/O TERM HV TERM HV TRI (No VTT)

HDSTBP[3:0]# I/O TERM HV TERM HV TRI (No VTT)

HDSTBN[3:0]# I/O TERM HV TERM HV TRI (No VTT)

HDINV[3:0]# I/O TERM HV TERM HV TRI (No VTT)

HADS# I/O TERM HV TERM HV TRI (No VTT)

HBNR# I/O TERM HV TERM HV TRI (No VTT)

HBPRI# O TERM HV TERM HV TRI (No VTT)

HDBSY# I/O TERM HV TERM HV TRI (No VTT)

HDEFER# O TERM HV TERM HV TRI (No VTT)

HDRDY# I/O TERM HV TERM HV TRI (No VTT)

HEDRDY# O TERM HV TERM HV TRI (No VTT)

Host I/F HHIT# I/O TERM HV TERM HV TRI (No VTT)

HHITM# I/O TERM HV TERM HV TRI (No VTT)

HLOCK# I/O TERM HV TERM HV TRI (No VTT)

HREQ[4:0]# I/O TERM HV TERM HV TRI (No VTT)

HTRDY# O TERM HV TERM HV TRI (No VTT)

HRS[2:0]# O TERM HV TERM HV TRI (No VTT)

HBREQ0# I/O TERM HV TERM HV TRI (No VTT)

HPCREQ# I TERM HV TERM HV TRI (No VTT)

HVREF I IN IN TRI

HRCOMP I/O TRI TRI after RCOMP TRI 20 Ω resistor

for board with

target

impedance of

60 Ω

HSWING I IN IN

HSCOMP I/O TRI TRI TRI

Loading...

Loading...