Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

146 Intel

®

82925X/82925XE MCH Datasheet

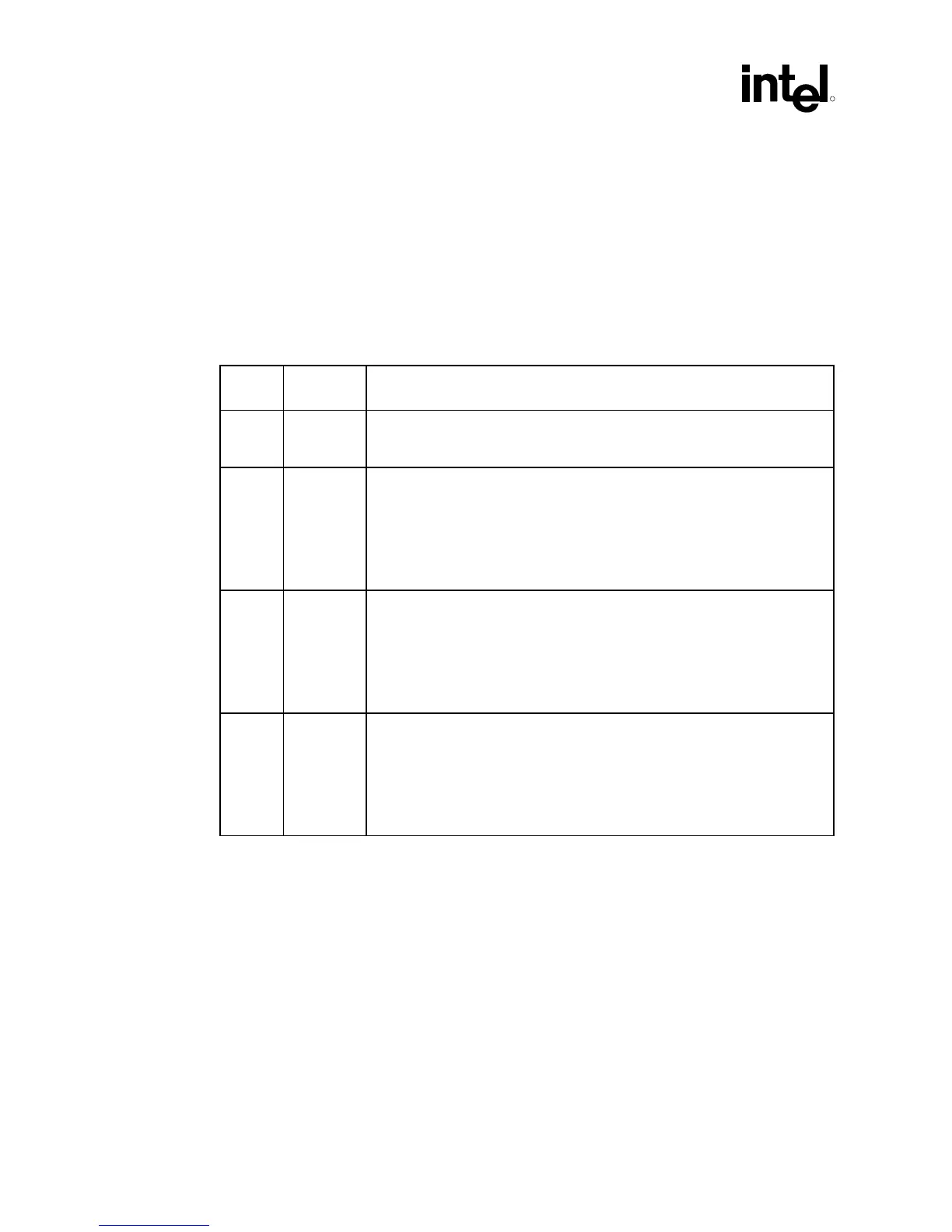

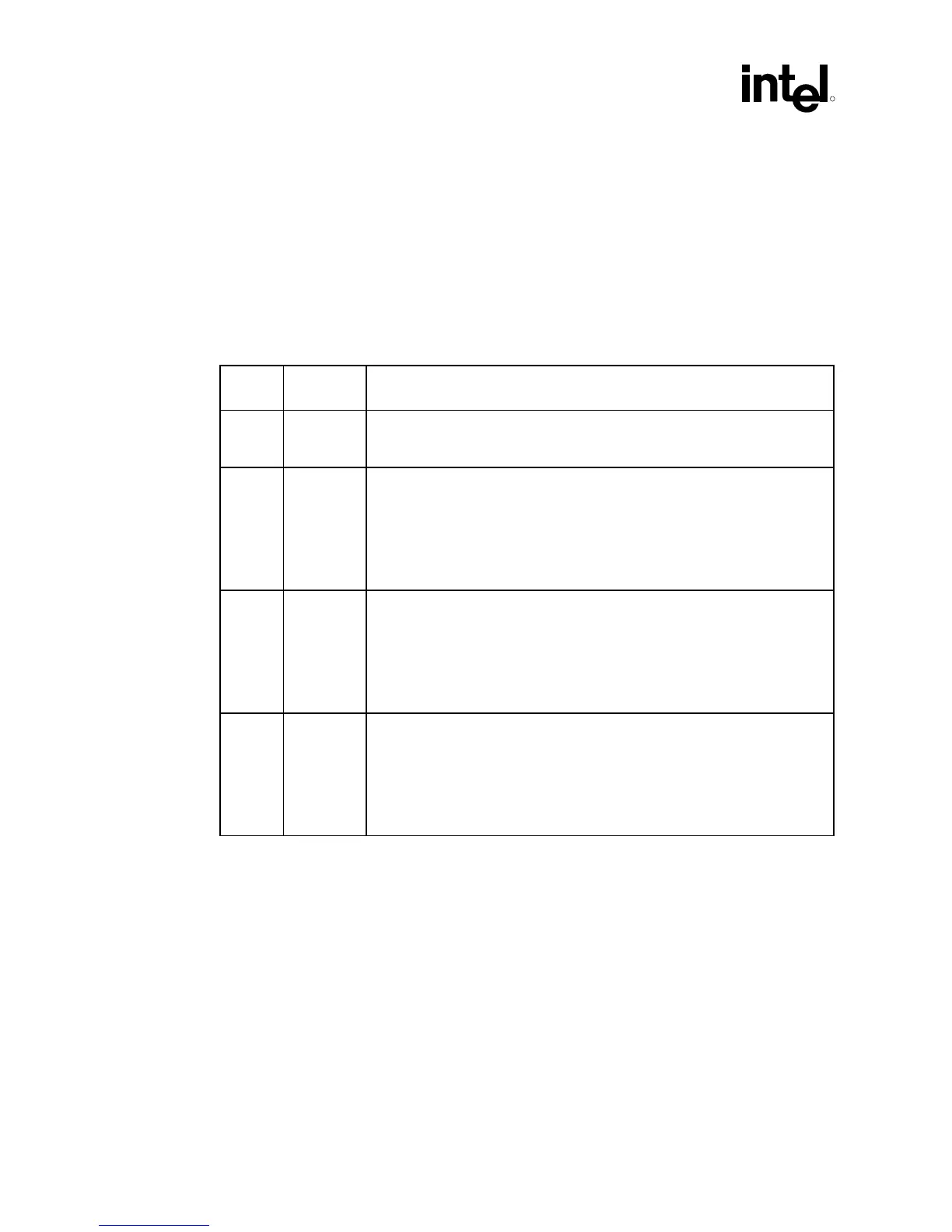

8.1.44 PEGLC—PCI Express*-G Legacy Control

PCI Device: 1

Address Offset: ECh

Default Value: 00000000h

Access: RO, R/W

Size: 32 bits

This register controls functionality that is needed by Legacy (non-PCI Express aware) OS’s

during run time.

Bit Access &

Default

Description

31:3 RO

0000

0000h

Reserved

2 R/W

0b

PME GPE Enable (PMEGPE):

0 = Do not generate GPE PME message when PME is received.

1 = Enable. Generate a GPE PME message when PME is received

(Assert_PMEGPE and Deassert_PMEGPE messages on DMI). This enables

the MCH to support PMEs on the PCI Express* x16 Graphics Interface port

under legacy OSs.

1 R/W

0b

Hot-Plug GPE Enable (HPGPE)

0 = Do not generate GPE Hot-Plug message when Hot-Plug event is received.

1 = Enable. Generate a GPE Hot-Plug message when Hot-Plug Event is received

(Assert_HPGPE and Deassert_HPGPE messages on DMI). This enables the

MCH to support Hot-Plug on the PCI Express* x16 Graphics Interface port

under legacy OSs.

0 R/W

0b

General Message GPE Enable (GENGPE)

0 = Do not forward received GPE assert/deassert messages.

1 = Enable. Forward received GPE assert/deassert messages. These general

GPE message can be received via the PCI Express* x16 Graphics Interface

port from an external Intel device and will be subsequently forwarded to the

Intel

®

ICH6 (via Assert_GPE and Deassert_GPE messages on DMI).

Loading...

Loading...