Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

144 Intel

®

82925X/82925XE MCH Datasheet

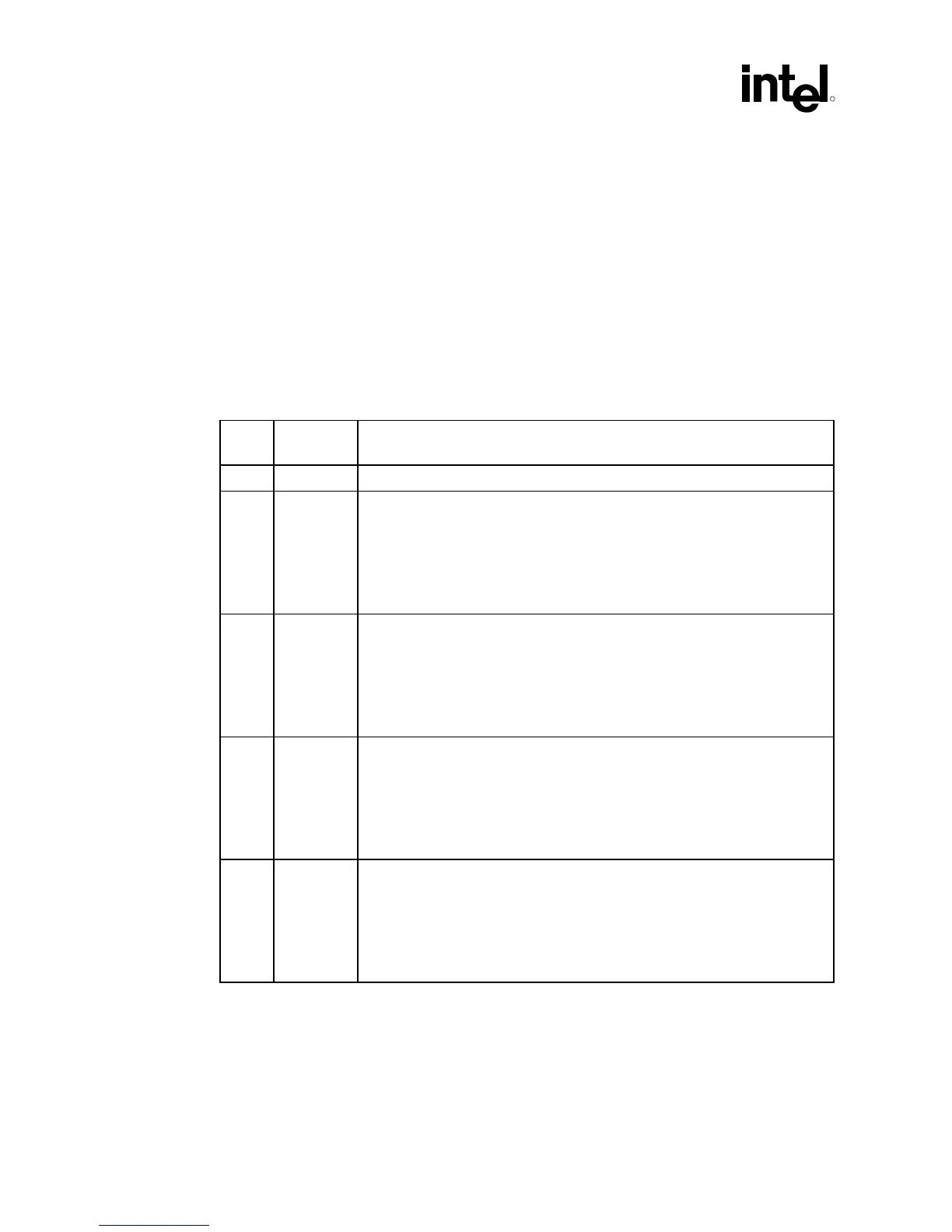

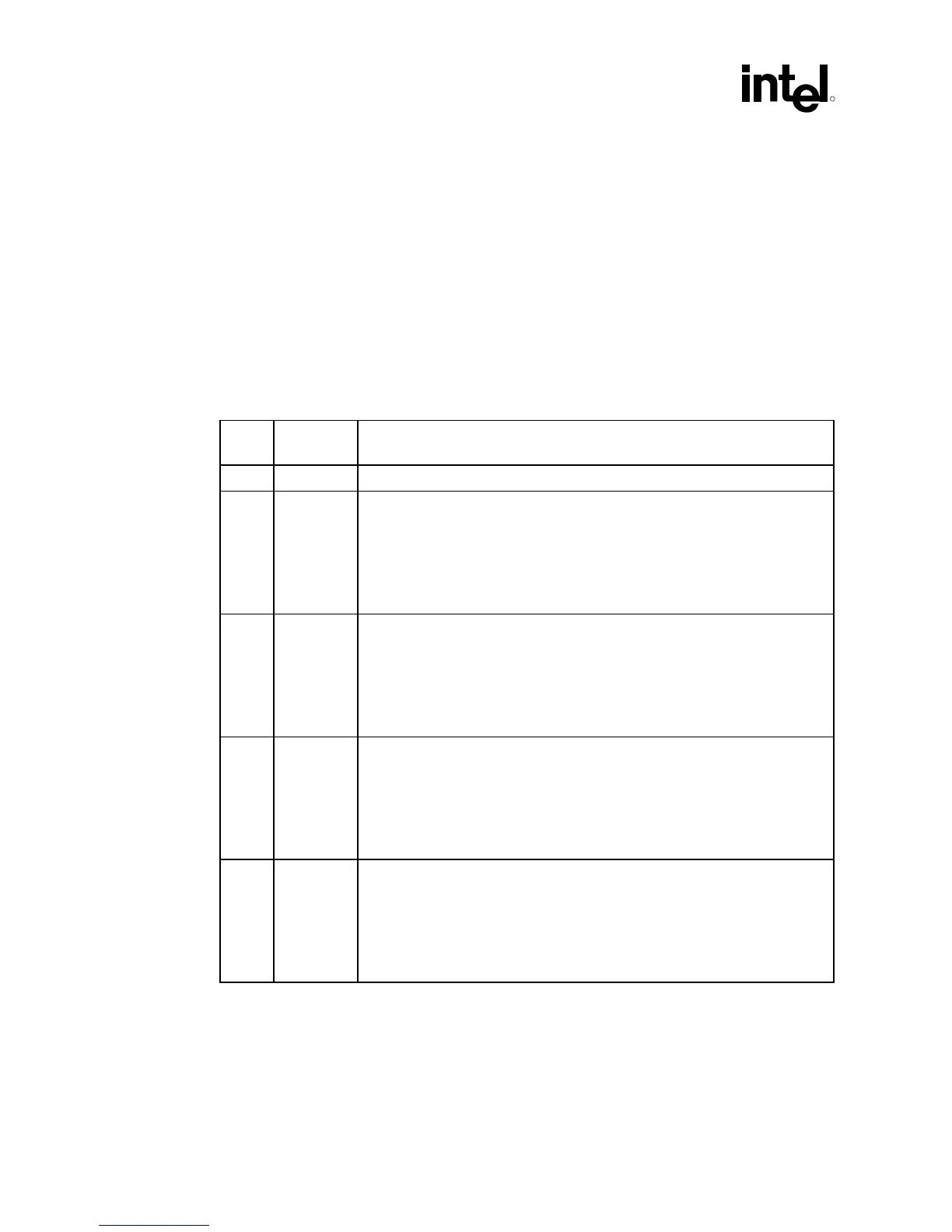

8.1.42 RCTL—Root Control (D1:F0)

PCI Device: 1

Address Offset: BCh

Default Value: 0000h

Access: R/W

Size: 16 bits

This register allows control of PCI Express Root Complex specific parameters. The system error

control bits in this register determine if corresponding SERRs are generated when our device

detects an error (reported in this device’s Device Status register) or when an error message is

received across the link. Reporting of SERR as controlled by these bits takes precedence over the

SERR Enable in the PCI Command Register.

Bit Access &

Default

Description

15:4 Reserved

3 R/W

0b

PME Interrupt Enable

0 = No interrupts are generated as a result of receiving PME messages.

1 = Enables interrupt generation upon receipt of a PME message as reflected in

the PME Status bit of the Root Status Register. A PME interrupt is also

generated if the PME Status bit of the Root Status Register is set when this bit

is set from a cleared state.

2 R/W

0b

System Error on Fatal Error Enable: This bit controls the Root Complex’s

response to fatal errors.

0 = No SERR generated on receipt of fatal error.

1 = Indicates that an SERR should be generated if a fatal error is reported by any

of the devices in the hierarchy associated with this Root Port, or by the Root

Port itself.

1 R/W

0b

System Error on Non-Fatal Uncorrectable Error Enable: This bit controls the

Root Complex’s response to non-fatal errors.

0 = No SERR generated on receipt of non-fatal error.

1 = Indicates that an SERR should be generated if a non-fatal error is reported by

any of the devices in the hierarchy associated with this Root Port, or by the

Root Port itself.

0 R/W

0b

System Error on Correctable Error Enable: This bit controls the Root Complex’s

response to correctable errors.

0 = No SERR generated on receipt of correctable error.

1 = Indicates that an SERR should be generated if a correctable error is reported

by any of the devices in the hierarchy associated with this Root Port, or by the

Root Port itself.

Loading...

Loading...