MCHBAR Registers

R

84 Intel

®

82925X/82925XE MCH Datasheet

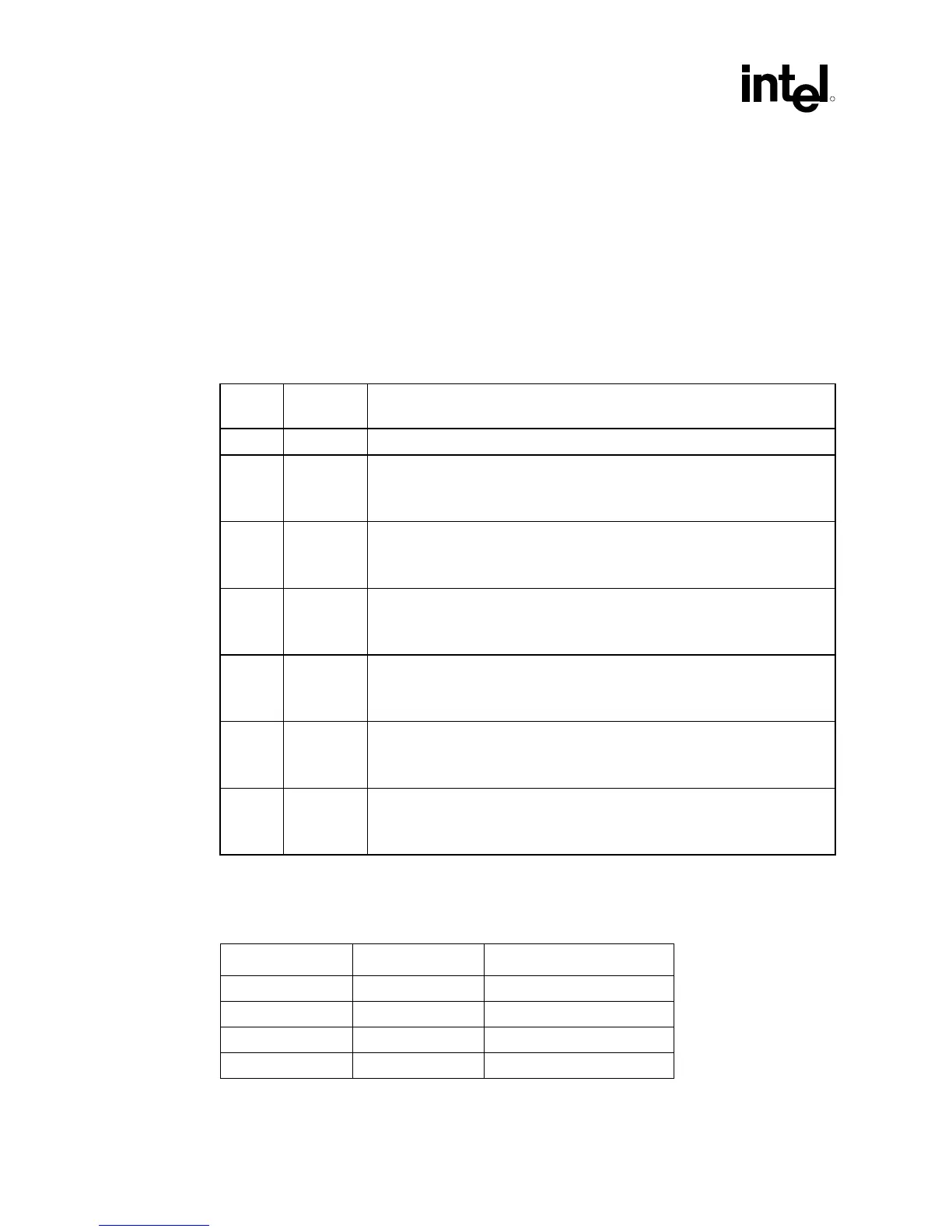

5.1.7 C0DCLKDIS—Channel A DRAM Clock Disable

MMIO Range: MCHBAR

Address Offset: 10Ch

Default Value: 00h

Access: R/W

Size: 8 bits

This register can be used to disable the system memory clock signals to each DIMM slot. This can

significantly reduce EMI and Power concerns for clocks that go to unpopulated DIMMs. Clocks

should be enabled based on whether a slot is populated, and what kind of DIMM is present.

Bit Access &

Default

Description

7:6 Reserved

5 R/W

0b

DIMM Clock Gate Enable Pair 5

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

4 R/W

0b

DIMM Clock Gate Enable Pair 4

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

3 R/W

0b

DIMM Clock Gate Enable Pair 3

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

2 R/W

0b

DIMM Clock Gate Enable Pair 2

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

1 R/W

0b

DIMM Clock Gate Enable Pair 1

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

0 R/W

0b

DIMM Clock Gate Enable Pair 0

0 = Tri-state the corresponding clock pair.

1 = Enable the corresponding clock pair.

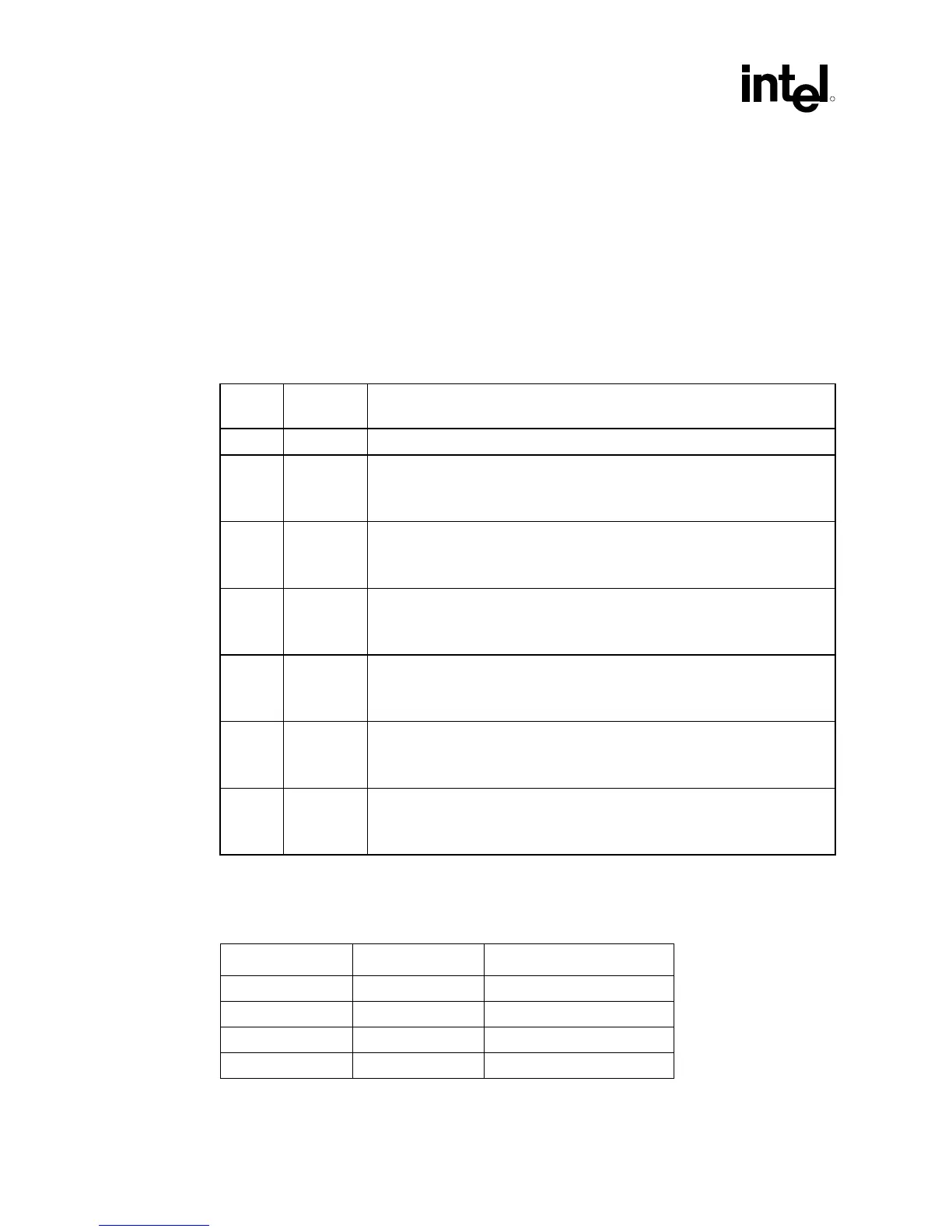

Note: Since there are multiple clock signals assigned to each Rank of a DIMM, it is important to clarify

exactly which Rank width field affects which clock signal:

Channel Rank Clocks Affected

0 0 or 1 SCLK_A[2:0]/ SCLK_A[2:0]#

0 2 or 3 SCLK_A[5:3]/ SCLK_A[5:3]#

1 0 or 1 SCLK_B[2:0]/ SCLK_B[2:0]#

1 2 or 3 SCLK_B[5:3]/ SCLK_B[5:3]#

Loading...

Loading...