Signal Description

R

Intel

®

82925X/82925XE MCH Datasheet 33

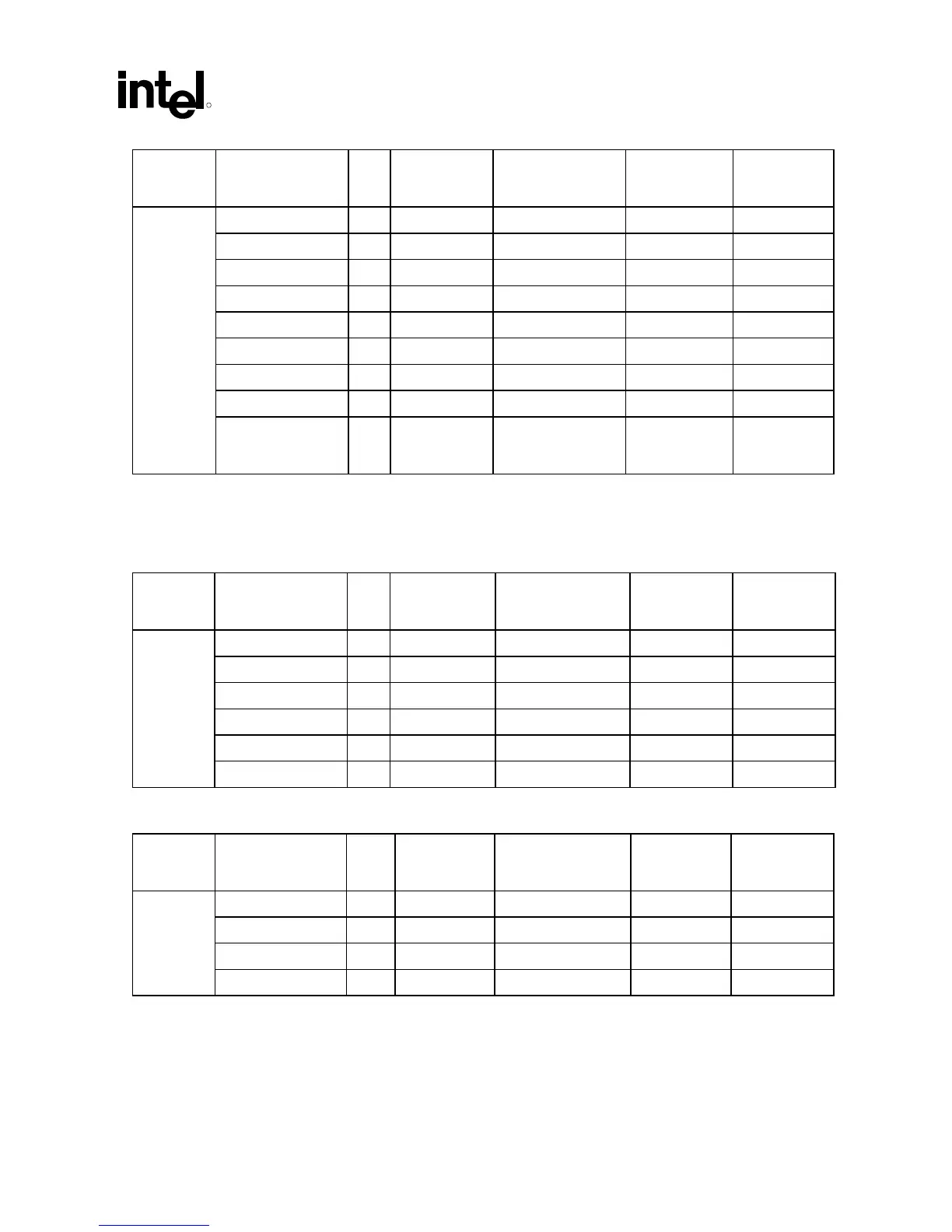

Interface Signal Name I/O

State During

RSTIN#

Assertion

State After

RSTIN# De-

assertion

S3

Pull-up/

Pull-down

SDQS_B[8:0]#

2

I/O TRI TRI TRI

SCKE_B[3:0] O LV LV LV

SODT_B[3:0] O LV LV LV

SRCOMP0 I/O TRI TRI (after RCOMP) TRI

SRCOMP1 I/O TRI TRI (after RCOMP) TRI

SM_SLEWIN[1:0] I IN IN IN

SM_SLEWOU[1:0] O TRI TRI (after RCOMP) TRI

SMVREF[1:0] I IN IN IN

SOCOMP[1:0] I/O TRI TRI TRI DDR2: 40 Ω

resistor to

ground

NOTES:

1. These signals are on the 82925X MCH only.

2. SDQS_A8/SDQS_A8# and SDQS_B8/SDQS_B8# are on the 82925X MCH only.

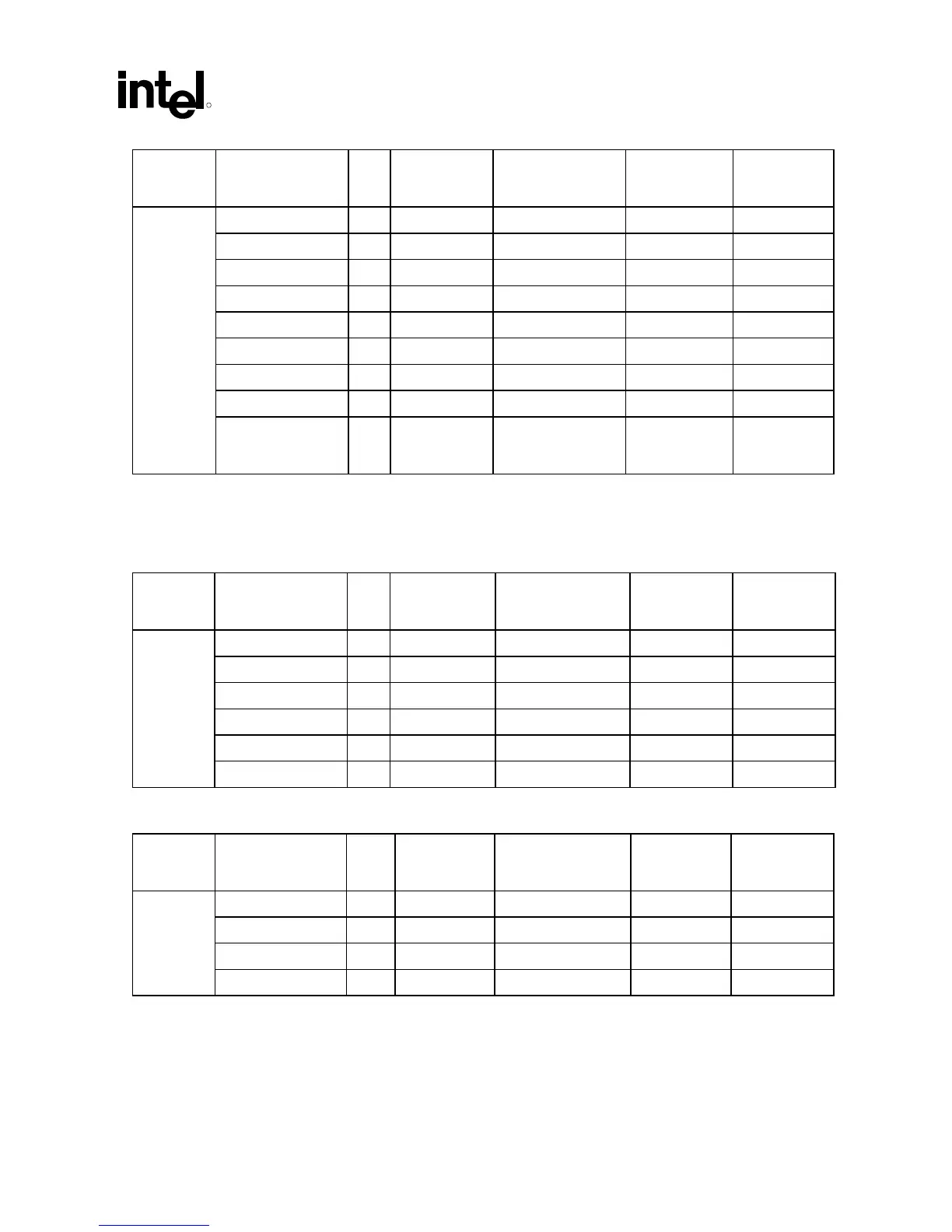

Table 2-3. PCI Express* Graphics x16 Port Reset and S3 States

Interface Signal Name I/O

State During

RSTIN#

Assertion

State After RSTIN#

De-assertion

S3

Pull-up/

Pull-down

EXP_RXN[15:0] I/O CMCT CMCT CMCT

EXP_RXP[15:0] I/O CMCT CMCT CMCT

EXP_TXN[15:0] O CMCT 1.0 V CMCT 1.0 V CMCT 1.0 V

EXP_TXP[15:0] O CMCT 1.0 V CMCT 1.0 V CMCT 1.0 V

EXP_COMPO I TRI TRI (after RCOMP) TRI

PCI

Express*-

Graphics

EXP_COMPI I TRI TRI (after RCOMP) TRI

Table 2-4. DMI Reset and S3 States

Interface Signal Name I/O

State During

RSTIN#

Assertion

State After RSTIN#

De-assertion

S3

Pull-up/ Pull-

down

DMI_RXN[3:0] I/O CMCT CMCT CMCT

DMI_RXP[3:0] I/O CMCT CMCT CMCT

DMI_TXN[3:0] O CMCT 1.0 V CMCT 1.0 V CMCT 1.0 V

DMI

DMI_TXP[3:0] O CMCT 1.0 V CMCT 1.0 V CMCT 1.0 V

Loading...

Loading...