MCHBAR Registers

R

88 Intel

®

82925X/82925XE MCH Datasheet

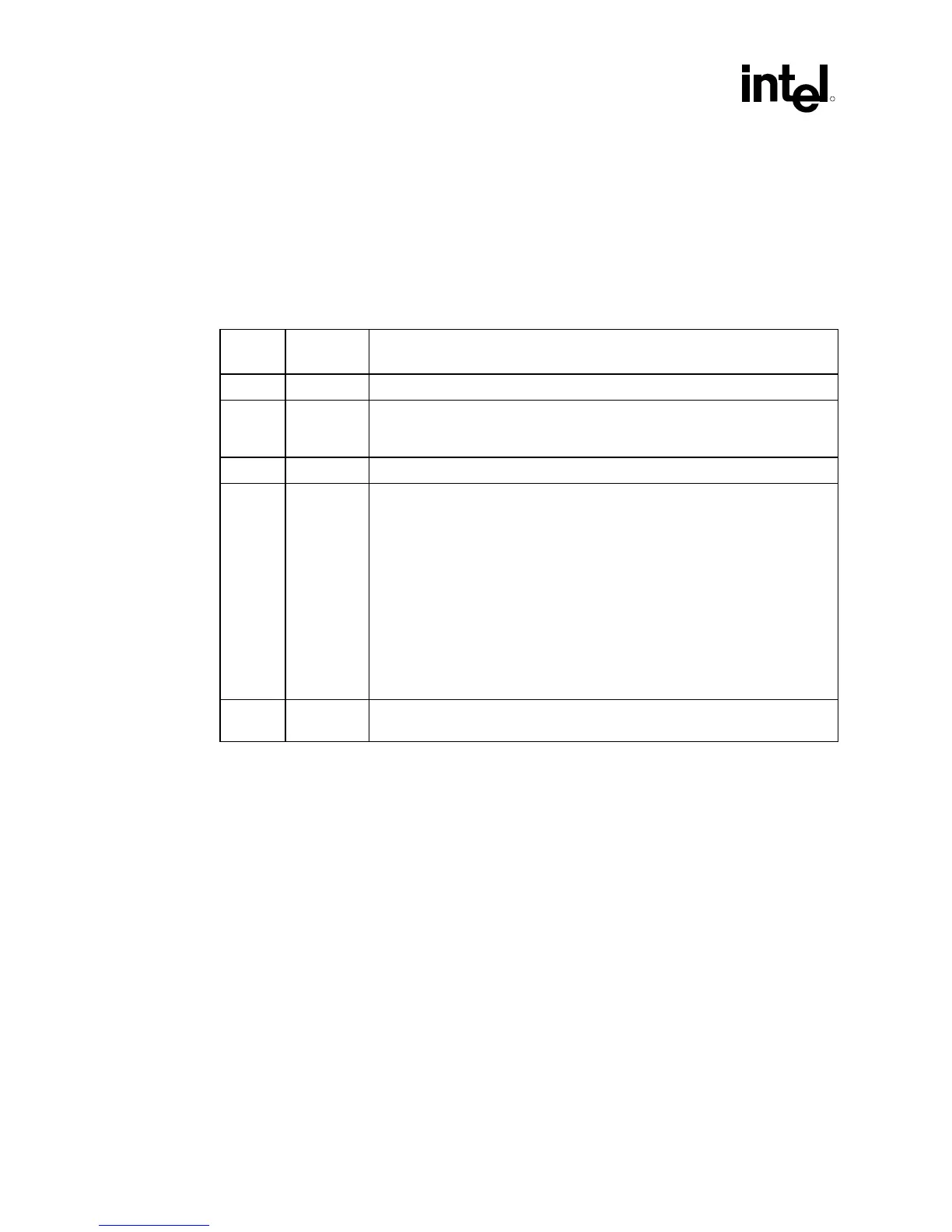

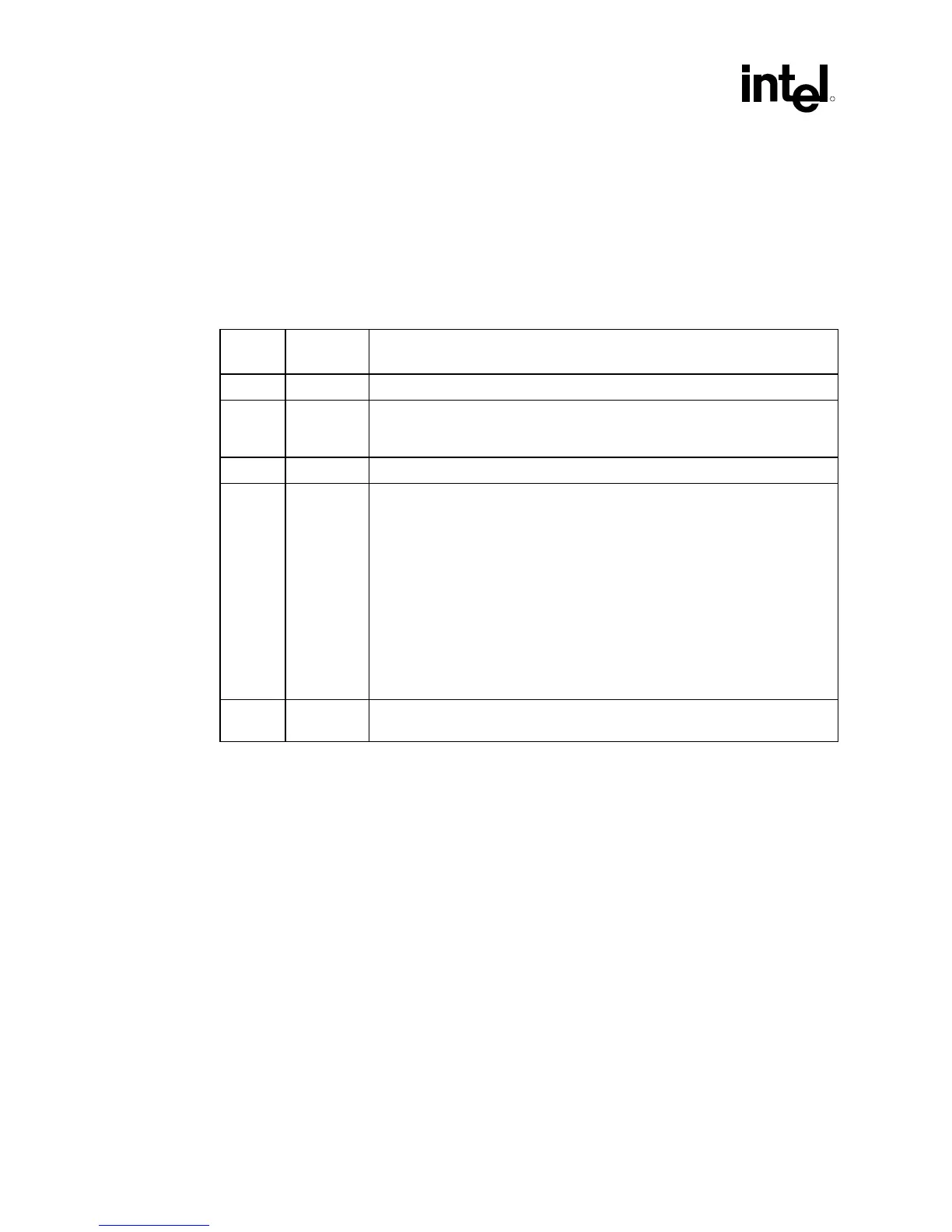

5.1.10 C0DRC0—Channel A DRAM Controller Mode 0

MMIO Range: MCHBAR

Address Offset: 120h

Default Value: 00000000h

Access: R/W

Size: 32 bits

Bit

Access &

Default

Description

31:30 Reserved

29 R/W

0b

Initialization Complete (IC): This bit is used for communication of software state

between the memory controller and the BIOS. BIOS sets this bit to 1 after

initialization of the DRAM memory array is complete.

28:11 Reserved

10:8 R/W

000b

Refresh Mode Select (RMS): This field determines whether refresh is enabled

and, if so, at what rate refreshes will be executed.

000 = Refresh disabled

001 = Refresh enabled. Refresh interval 15.6 µsec

010 = Refresh enabled. Refresh interval 7.8 µsec

011 = Refresh enabled. Refresh interval 3.9 µsec

100 = Refresh enabled. Refresh interval 1.95 µsec

111 = Refresh enabled. Refresh interval 64 clocks (fast refresh mode)

Other = Reserved

7 RO

0b

Reserved

Loading...

Loading...