Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

126 Intel

®

82925X/82925XE MCH Datasheet

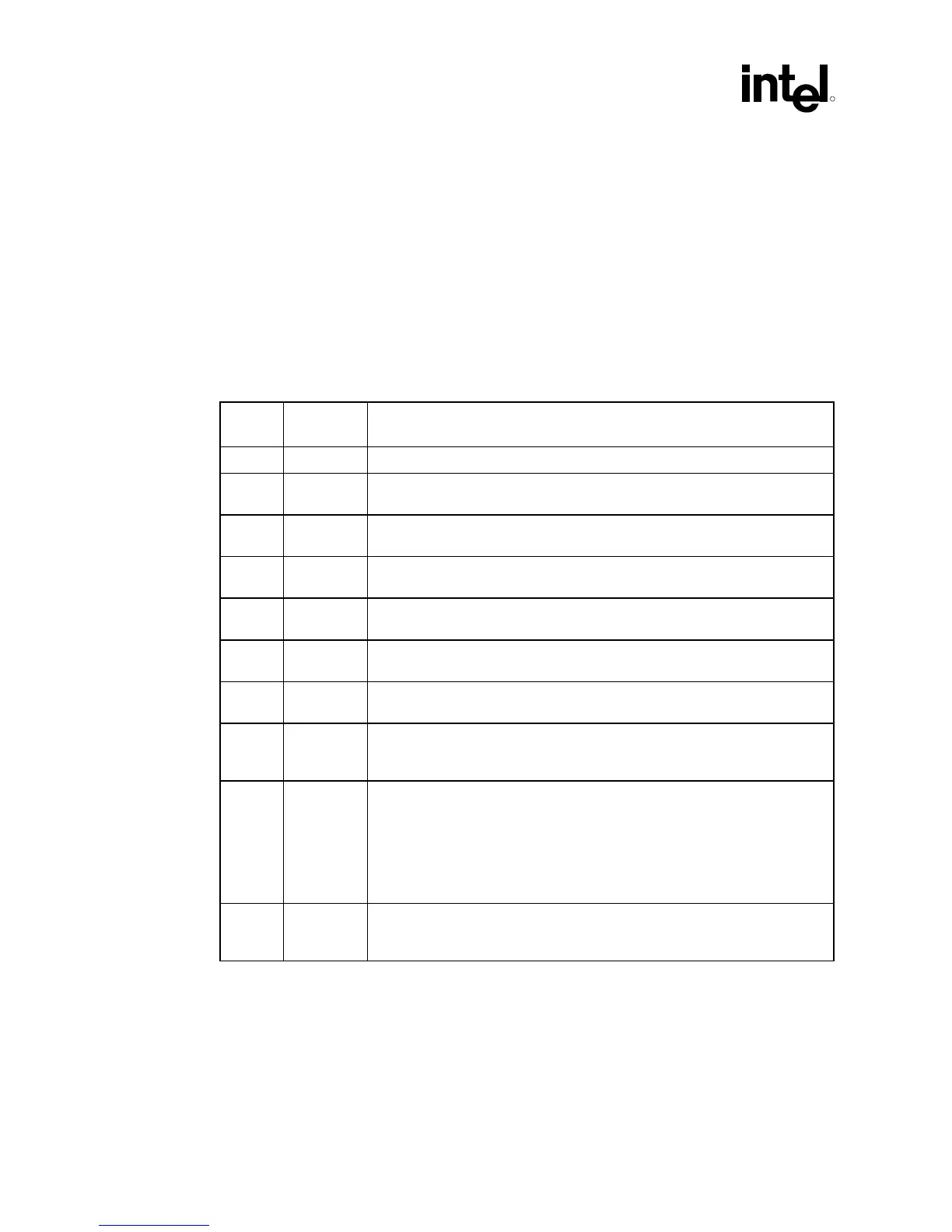

8.1.22 BCTRL1—Bridge Control (D1:F0)

PCI Device: 1

Address Offset: 3Eh

Default Value: 0000h

Access: RO, R/W

Size: 16 bits

This register provides extensions to the PCICMD1 register that are specific to PCI-PCI bridges.

The BCTRL provides additional control for the secondary interface (i.e., PCI Express) as well as

some bits that affect the overall behavior of the “virtual” Host-PCI Express bridge embedded

within MCH (e.g., VGA compatible address ranges mapping).

Bit Access &

Default

Description

15:12 Reserved

11 RO

0b

Discard Timer SERR Enable: Hardwired to 0.

10 RO

0b

Discard Timer Status: Hardwired to 0.

9 RO

0b

Secondary Discard Timer: Hardwired to 0.

8 RO

0b

Primary Discard Timer: Hardwired to 0.

7 RO

0b

Fast Back-to-Back Enable (FB2BEN): Hardwired to 0.

6 R/W

0b

Secondary Bus Reset (SRESET): Setting this bit triggers a hot reset on the

corresponding PCI Express* Port.

5 RO

0b

Master Abort Mode (MAMODE): When acting as a master, unclaimed reads

that experience a master abort returns all 1s and any writes that experience a

master abort completes normally and the data is thrown away. Hardwired to 0.

4 R/W

0b

VGA 16-bit Decode: This bit enables the PCI-to-PCI bridge to provide 16-bit

decoding of VGA I/O address precluding the decoding of alias addresses every 1

KB. This bit only has meaning if bit 3 (VGA Enable) of this register is also set to

1, enabling VGA I/O decoding and forwarding by the bridge.

0 = Execute 10-bit address decodes on VGA I/O accesses.

1 = Execute 16-bit address decodes on VGA I/O accesses.

3 R/W

0b

VGA Enable (VGAEN): This bit controls the routing of processor-initiated

transactions targeting VGA compatible I/O and memory address ranges. See the

VGAEN/MDAP table in Device 0, offset 97h[0].

Loading...

Loading...