Introduction

R

Intel

®

82925X/82925XE MCH Datasheet 15

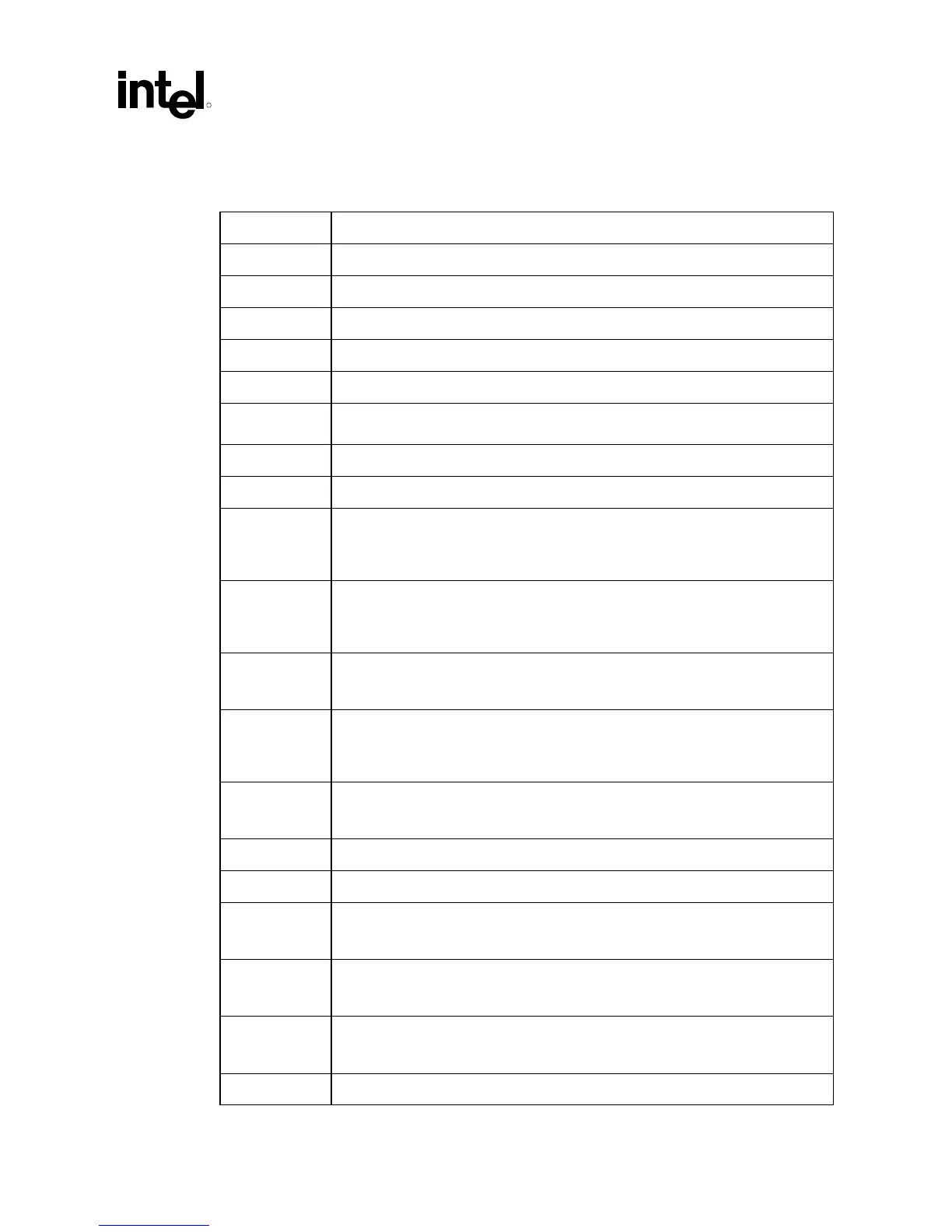

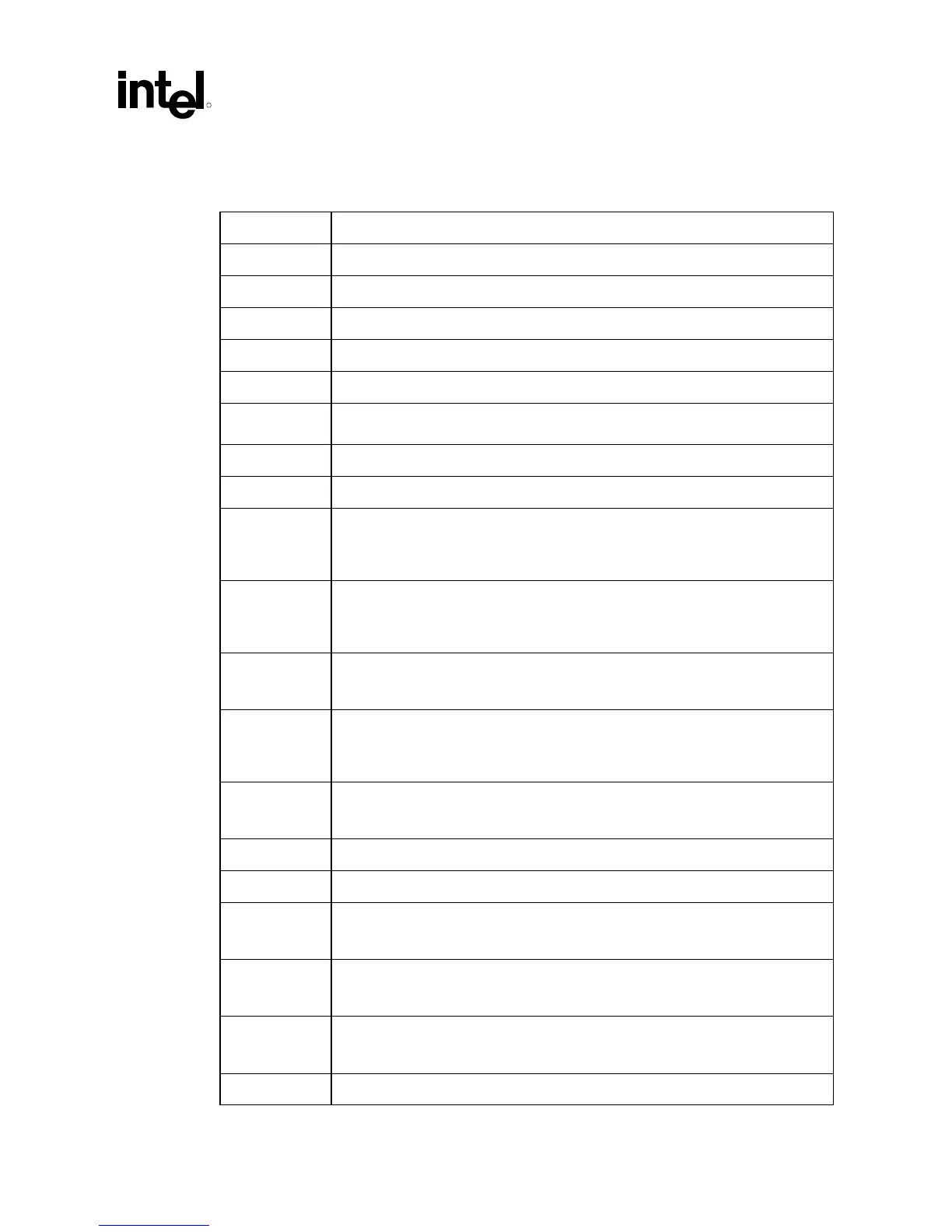

1.1 Terminology

Term Description

Core

Core refers to the internal base logic in the MCH.

DBI

Dynamic Bus Inversion.

DDR2

A second generation Double Data Rate SDRAM memory technology.

DMI

The Direct Media Interface is the connection between the MCH and the Intel

®

ICH6.

FSB

Front Side Bus. The FSB is synonymous with Host or processor bus

Full Reset

Full reset is when PWROK is de-asserted. Warm reset is when both RSTIN# and

PWROK are asserted.

Host

This term is used synonymously with processor.

INTx

An interrupt request signal where X stands for interrupts A,B,C and D.

Intel

®

ICH6

Sixth generation I/O Controller Hub component that contains additional functionality

compared to previous ICH6s. The Intel

®

I/O Controller Hub component contains the

primary PCI interface, LPC interface, USB2, ATA-100, and other I/O functions. It

communicates with the MCH over a proprietary interconnect called DMI.

MCH

The Memory Controller Hub (MCH) component contains the processor interface and

DRAM controller. It may also contain an x16 PCI Express port (typically the external

graphics interface). It communicates with the I/O controller hub (ICH6*) and other I/O

controller hubs over the DMI interconnect.

MSI

Message Signaled Interrupt. A transaction initiated outside the host, conveying interrupt

information to the receiving agent through the same path that normally carries read and

write commands.

PCI Express*

Third Generation Input Output (PCI Express) Graphics Attach called PCI Express

Graphics. A high-speed serial interface whose configuration is software compatible with

the existing PCI specifications. The specific PCI Express implementation intended for

connecting the MCH to an external graphics controller is a x16 link and replaces AGP.

Primary PCI

The physical PCI bus that is driven directly by the ICH6 component. Communication

between Primary PCI and the MCH occurs over DMI. Note that the Primary PCI bus is

not PCI Bus 0 from a configuration standpoint.

SCI

System Control Interrupt. SCI is used in ACPI protocol.

SERR

An indication that an unrecoverable error has occurred on an I/O bus.

SMI

System Management Interrupt. SMI is used to indicate any of several system conditions

(such as thermal sensor events, throttling activated, access to System Management

RAM, chassis open, or other system state related activity).

Rank

A unit of DRAM corresponding to eight x8 SDRAM devices in parallel or four x16

SDRAM devices in parallel, ignoring ECC. These devices are usually, but not always,

mounted on a single side of a DIMM.

TOLM

Top Of Low Memory. The highest address below 4 GB for which a processor-initiated

memory read or write transaction will create a corresponding cycle to DRAM on the

memory interface.

VCO

Voltage Controlled Oscillator.

Loading...

Loading...