Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

Intel

®

82925X/82925XE MCH Datasheet 155

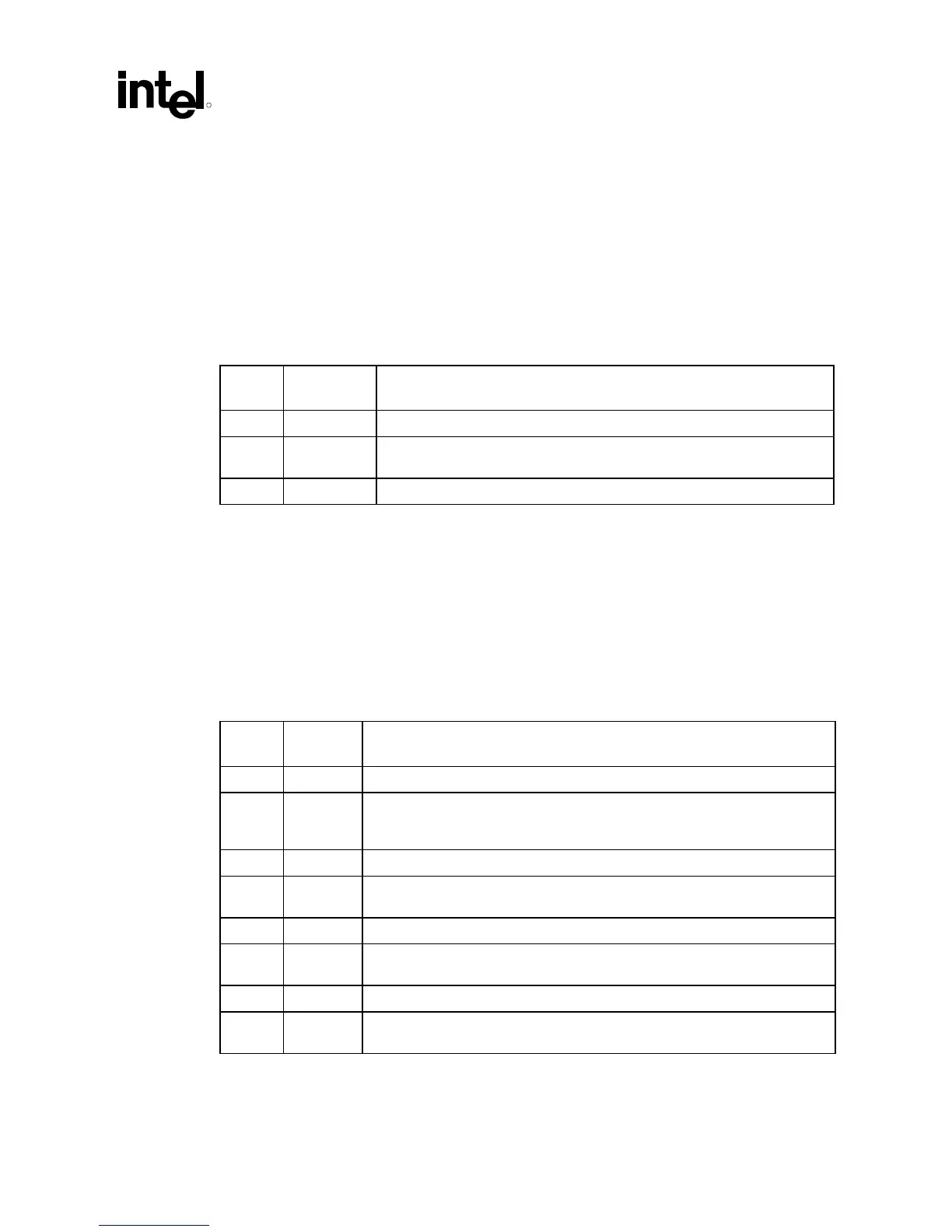

8.1.58 LE1A—Link Entry 1 Address (D1:F0)

PCI Device: 1

Address Offset: 158h

Default Value: 0000000000000000h

Access: R/WO

Size: 64 bits

This register provides the second part of a Link Entry that declares an internal link to another

Root Complex Element.

Bit Access &

Default

Description

63:32 Reserved

31:12 R/WO

0 0000h

Link Address: This field indicates memory-mapped base address of the RCRB

that is the target element (Egress Port) for this link entry.

11:0 Reserved

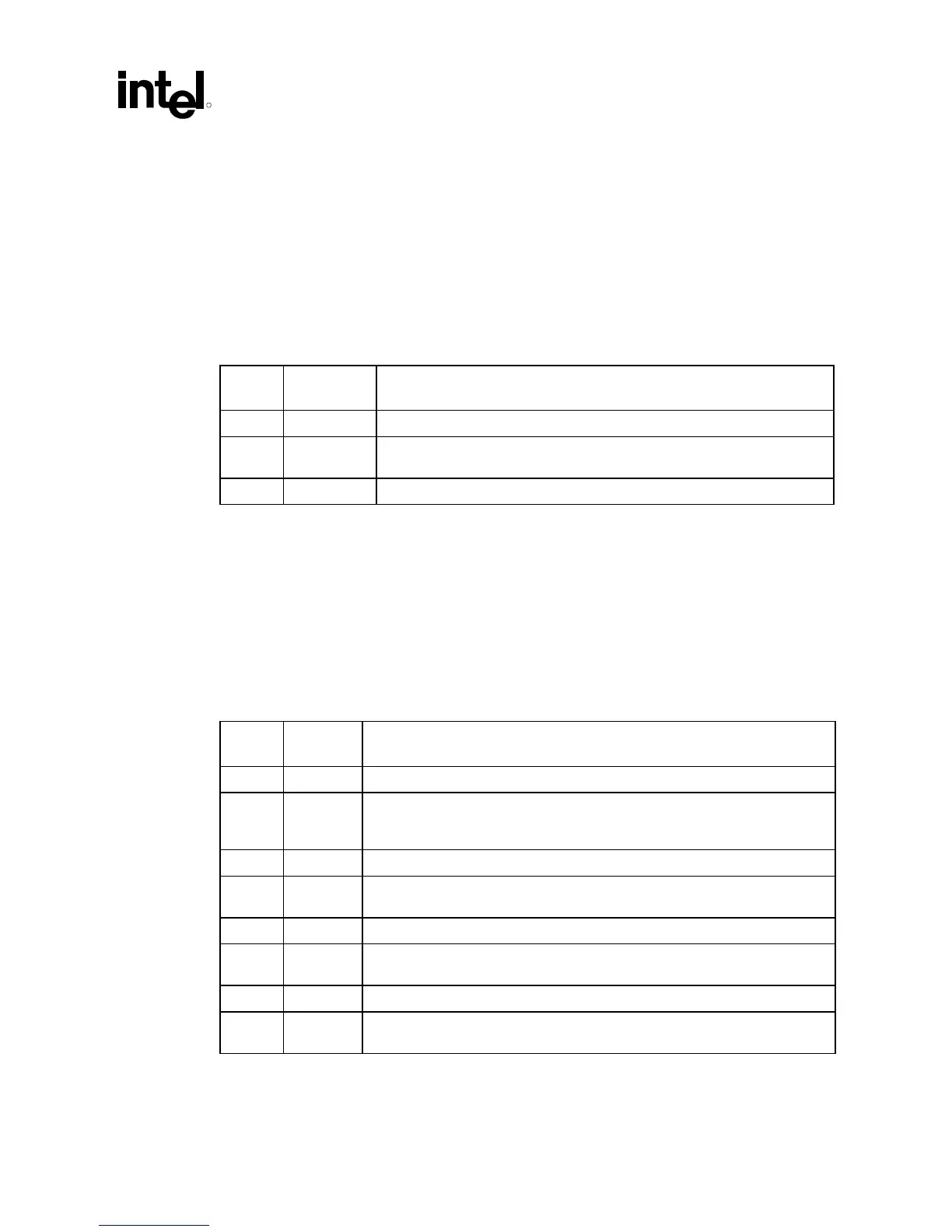

8.1.59 PEGSSTS—PCI Express*-G Sequence Status (D1:F0)

PCI Device: 1

Address Offset: 218h

Default Value: 0000000000000FFFh

Access: RO

Size: 64 bits

This register provides PCI Express status reporting that is required by the PCI Express

specification.

Bit Access &

Default

Description

63:60 Reserved

59:48 RO

000h

Next Transmit Sequence Number: Value of the NXT_TRANS_SEQ counter.

This counter represents the transmit Sequence number to be applied to the next

TLP to be transmitted onto the Link for the first time.

47:44 Reserved

43:32 RO

000h

Next Packet Sequence Number: Packet sequence number to be applied to the

next TLP to be transmitted or re-transmitted onto the Link.

31:28 Reserved

27:16 RO

000h

Next Receive Sequence Number: This is the sequence number associated with

the TLP that is expected to be received next.

15:12 Reserved

11:0 RO

FFFh

Last Acknowledged Sequence Number: This is the sequence number

associated with the last acknowledged TLP.

§

Loading...

Loading...