Host Bridge/DRAM Controller Registers (D0:F0)

R

54 Intel

®

82925X/82925XE MCH Datasheet

4.1.12 EPBAR—Egress Port Base Address (D0:F0)

PCI Device: 0

Address Offset: 40h

Default Value: 00000000h

Access: RO

Size: 32 bits

This is the base address for the Egress Port MMIO configuration space. There is no physical

memory within this 4-KB window that can be addressed. The 4 KB reserved by this register does

not alias to any PCI 2.3 compliant memory mapped space.

On reset, this register is disabled and must be enabled by writing a 1 to EPBAREN[Dev 0, offset

54h, bit 27]

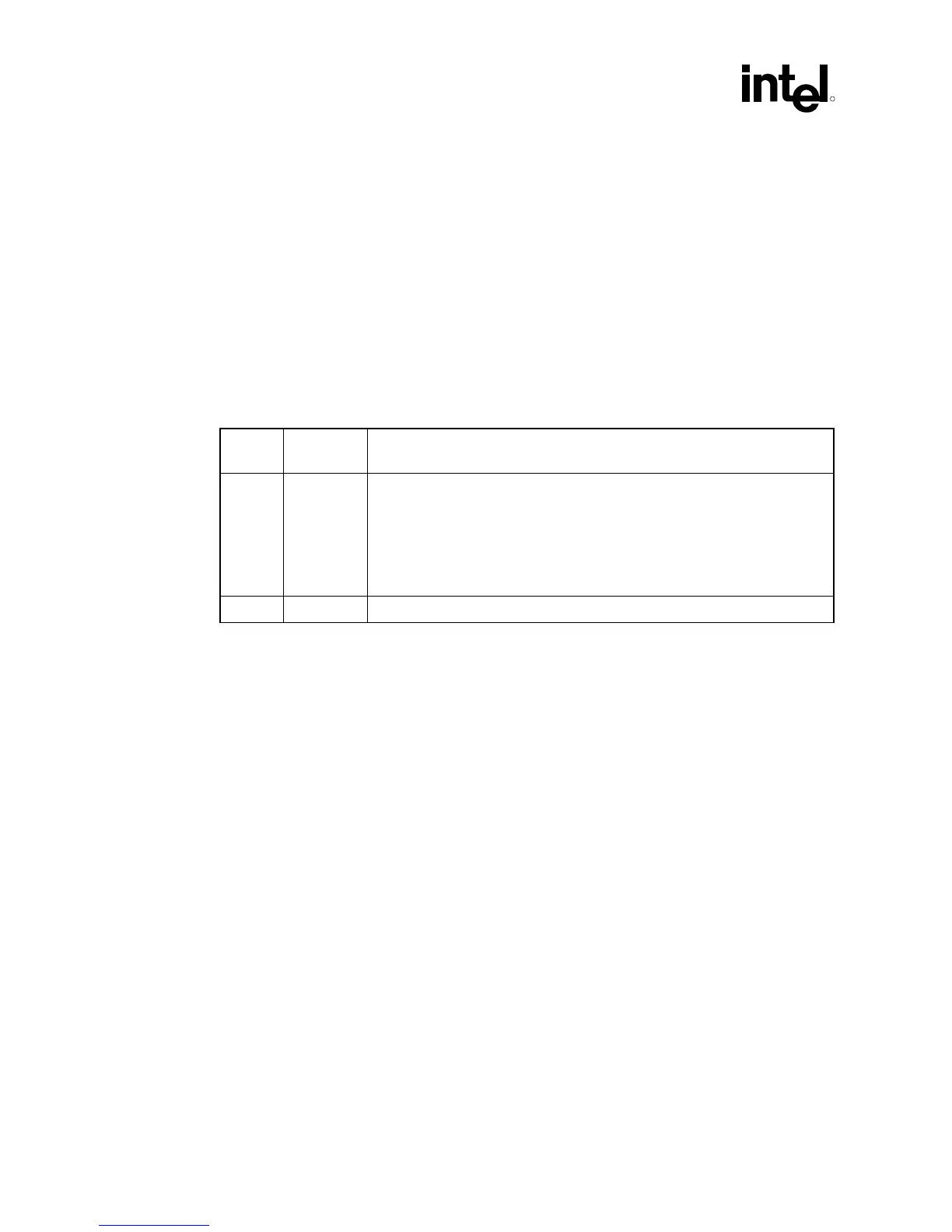

Bit Access &

Default

Description

31:12 R/W

00000h

Egress Port MMIO Base Address: This field corresponds to bits 31 to 12 of the

base address Egress Port MMIO configuration space.

BIOS will program this register resulting in a base address for a 4-KB block of

contiguous memory address space. This register ensures that a naturally aligned

4-KB space is allocated within total addressable memory space of 4 GB.

System software uses this base address to program the MCH MMIO register set.

11:0 Reserved

Loading...

Loading...