Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

Intel

®

82925X/82925XE MCH Datasheet 131

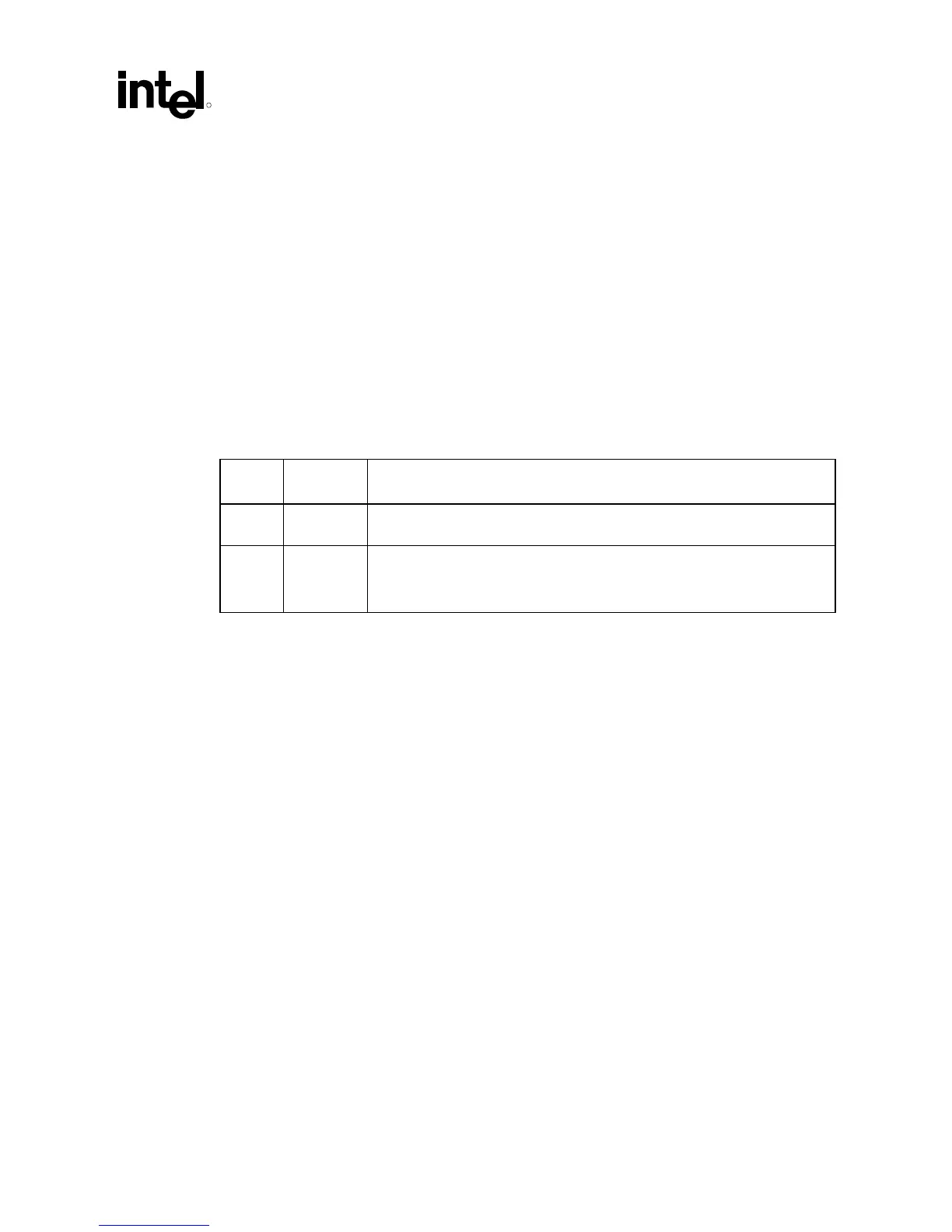

8.1.27 MSI_CAPID—Message Signaled Interrupts Capability ID

(D1:F0)

PCI Device: 1

Address Offset: 90h

Default Value: A005h

Access: RO

Size: 16 bits

When a device supports MSI, it can generate an interrupt request to the processor by writing a

predefined data item (a message) to a predefined memory address.

The reporting of the existence of this capability can be disabled by setting MSICH (CAPL [0] @

7Fh). In that case walking this linked list will skip this capability and, instead, go directly from

the PCI PM capability to the PCI Express capability.

Bit Access &

Default

Description

15:8 RO

A0h

Pointer to Next Capability: This field contains a pointer to the next item in the

capabilities list that is the PCI Express* capability.

7:0 RO

05h

Capability ID:

05h = Identifies this linked list item (capability structure) as being for MSI

registers.

Loading...

Loading...