Signal Description

R

Intel

®

82925X/82925XE MCH Datasheet 29

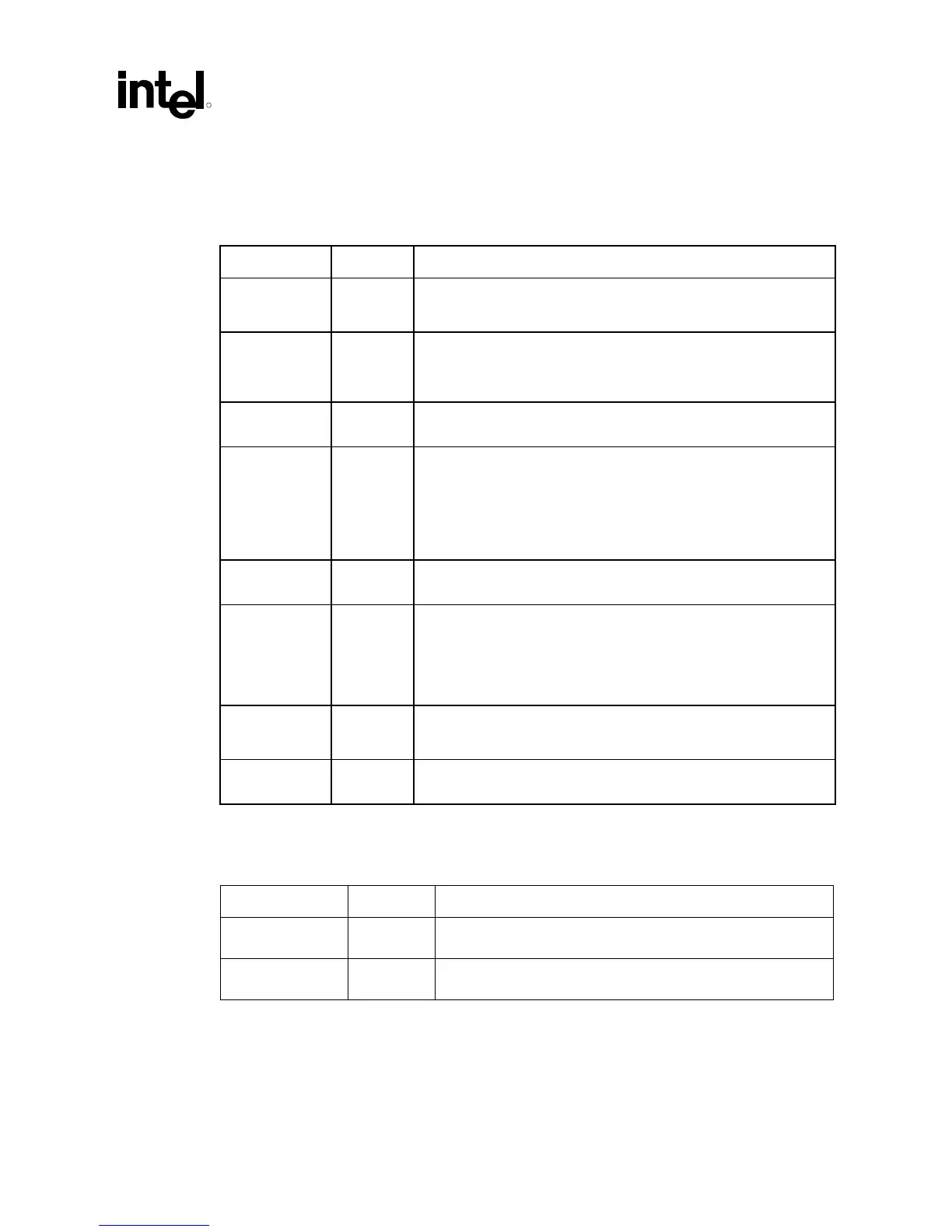

2.6 Clocks, Reset, and Miscellaneous

Signal Name Type Description

HCLKP

HCLKN

I

CMOS

Differential Host Clock In: These pins receive a differential host clock

from the external clock synthesizer. This clock is used by all of the MCH

logic that is in the Host clock domain.

GCLKP

GCLKN

I

CMOS

Differential PCI Express Graphics Clock In: These pins receive a

differential 100 MHz serial reference clock from the external clock

synthesizer. This clock is used to generate the clocks necessary for the

support of PCI Express.

DREFCLKN

DREFCLKP

I

CMOS

Display PLL Differential Clock In

RSTIN# I

HVIN

Reset In: When asserted, this signal will asynchronously reset the MCH

logic. This signal is connected to the PLTRST# output of the Intel

®

ICH6.

All PCI Express Graphics Attach output signals will also tri-state

compatible with PCI Express* Specification Rev 1.0a.

This input should have a Schmitt trigger to avoid spurious resets.

This signal is required to be 3.3 V tolerant.

PWROK I

HVIN

Power OK: When asserted, PWROK is an indication to the MCH that

core power has been stable for at least 10 us.

EXTTS# I

HVCMOS

External Thermal Sensor Input: This signal may connect to a precision

thermal sensor located on or near the DIMMs. If the system temperature

reaches a dangerously high value, then this signal can be used to trigger

the start of system thermal management. This signal is activated when

an increase in temperature causes a voltage to cross some threshold in

the sensor.

MTYPE I

CMOS

Memory Type Select Strap. This signal is a strapping option that

indicates the type of system memory. This signal should be tied to

ground indicating DDR2 memory.

ICH_SYNC# O

HVCMOS

ICH Sync: This signal is connected to the MCH_SYNCH# signal on the

ICH6.

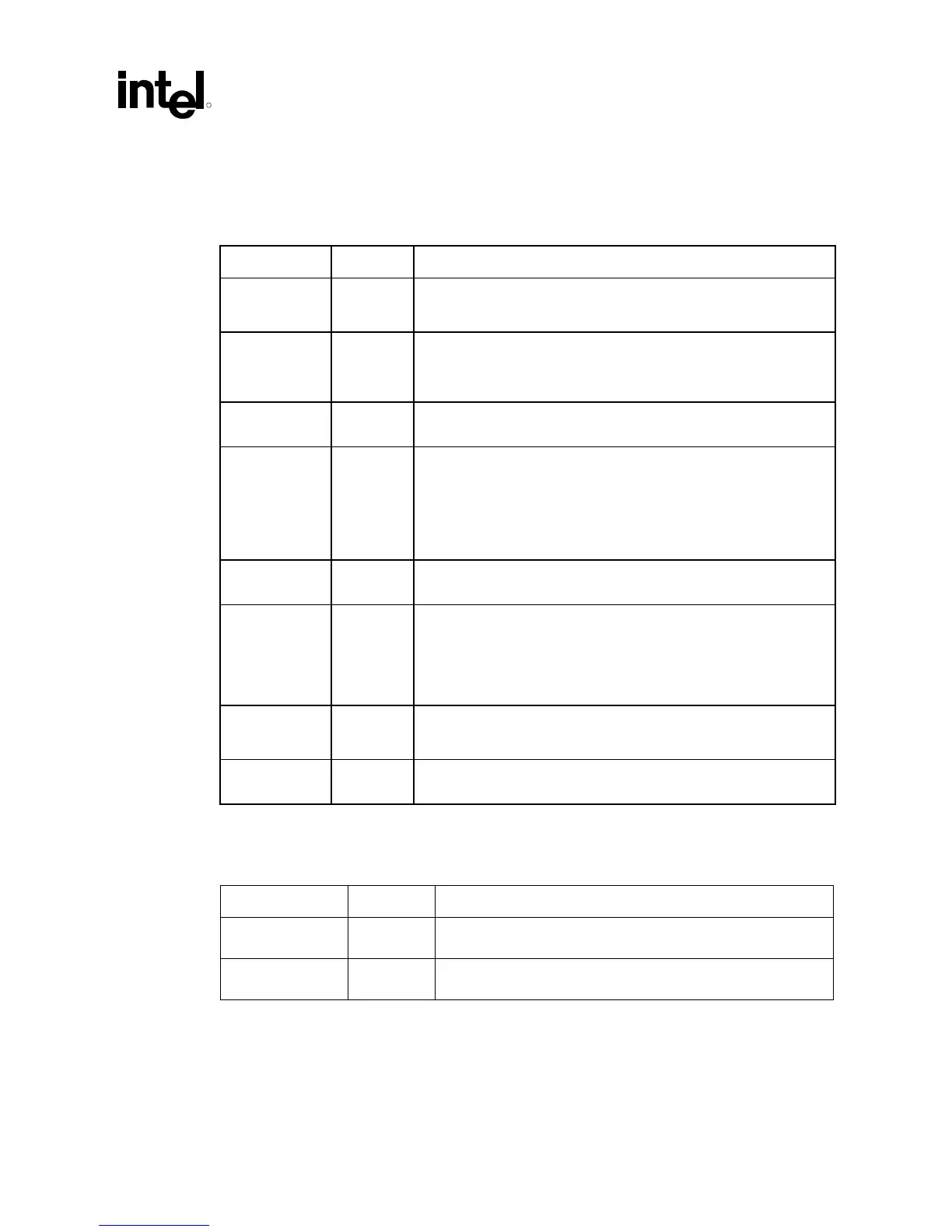

2.7 Direct Media Interface (DMI)

Signal Name Type Description

DMI_RXP[3:0]

DMI_RXN[3:0]

I/O

DMI

Direct Media Interface: These signals are the receive differential

pair (Rx).

DMI_TXP[3:0]

DMI_TXN[3:0]

O

DMI

Direct Media Interface: These signals are the transmit differential

pair (Tx).

Loading...

Loading...