Host-PCI Express* Graphics Bridge Registers (D1:F0)

R

140 Intel

®

82925X/82925XE MCH Datasheet

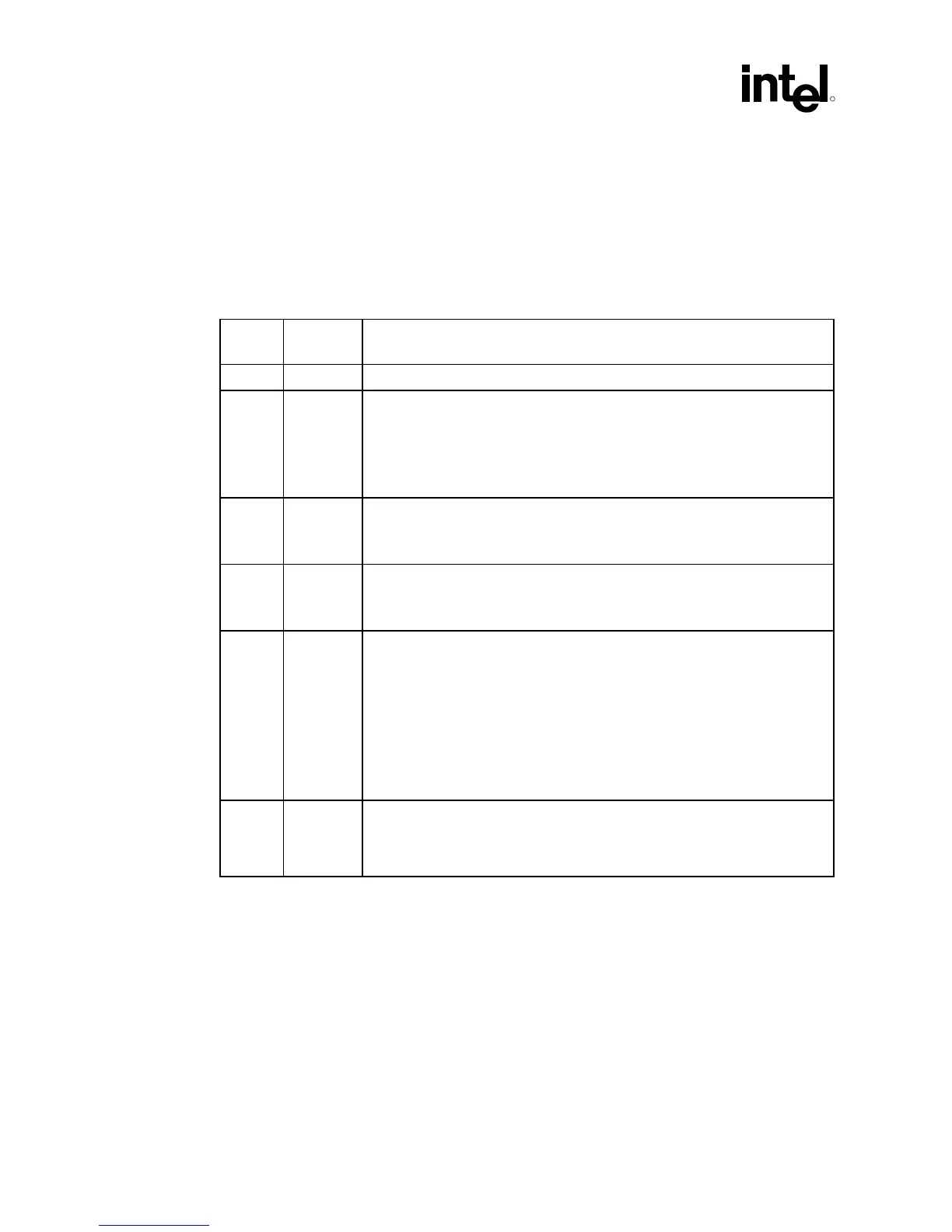

8.1.38 LSTS—Link Status (D1:F0)

PCI Device: 1

Address Offset: B2h

Default Value: 1001h

Access: RO

Size: 16 bits

This register indicates PCI Express link status.

Bit Access &

Default

Description

15:13 Reserved

12 RO

1b

Slot Clock Configuration

0 = The device uses an independent clock irrespective of the presence of a

reference on the connector.

1 = The device uses the same physical reference clock that the platform provides

on the connector.

11 RO

0b

Link Training:

1 = Link training is in progress. Hardware clears this bit once Link training is

complete.

10 RO

0b

Training Error:

1 = This bit is set by hardware upon detection of unsuccessful training of the Link

to the L0 Link state.

9:4 RO

00h

Negotiated Width: This field indicates negotiated link width. This field is valid

only when the link is in the L0, L0s, or L1 states (after link width negotiation is

successfully completed).

00h = Reserved

01h = X1

04h = Reserved

08h = Reserved

10h = X16

All other encodings are reserved.

3:0 RO

1h

Negotiated Speed: This field indicates negotiated link speed.

1h = 2.5 Gb/s

All other encodings are reserved.

Loading...

Loading...