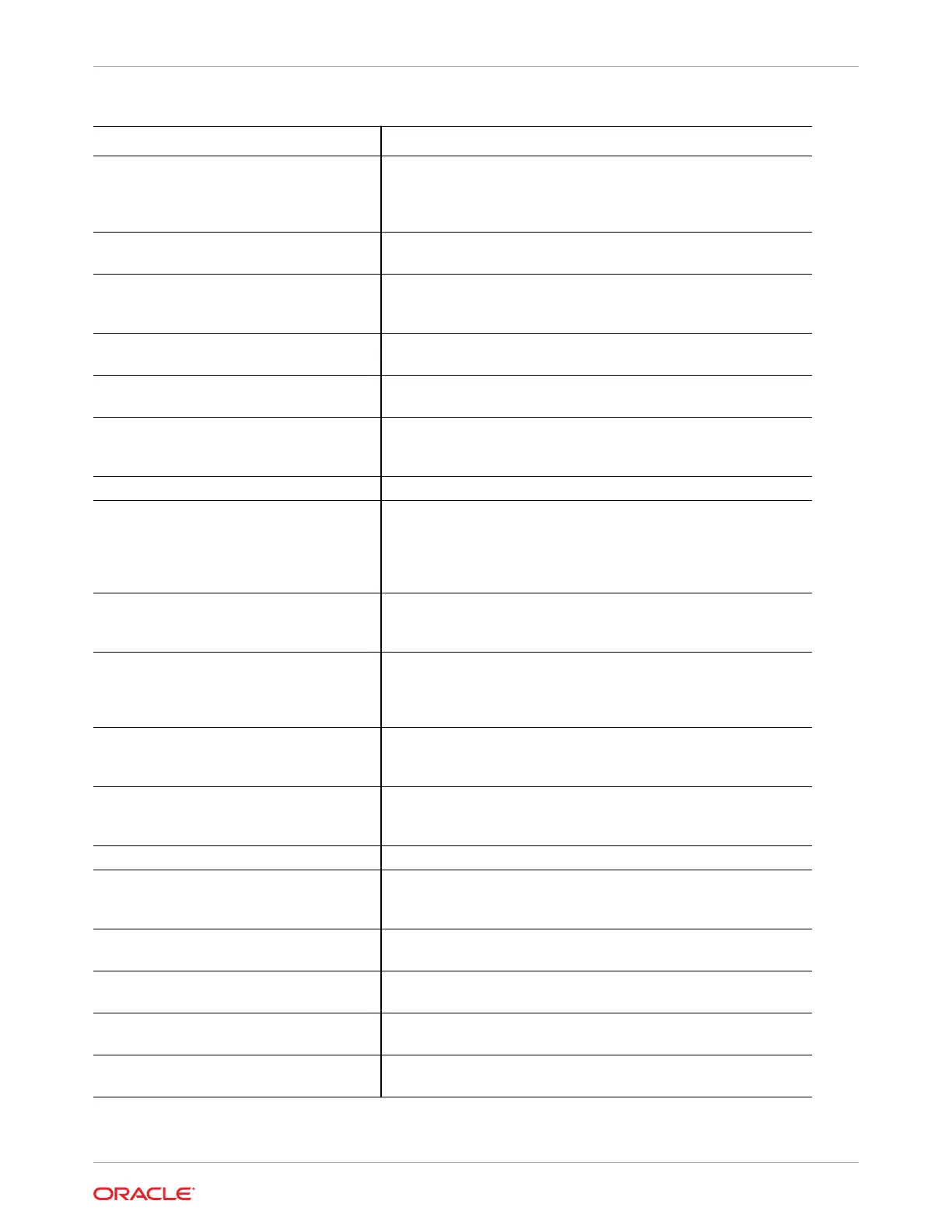

PCI Subsystem Settings Description

AtomicOp Requester Enable If supported by hardware and enabled, Atomic Operation

(AtomicOp) Requester initiates AtomicOp Requests only if the Bus

Master Enable bit is in the Command Register Set. Default is

Disabled.

AtomicOp Egress Blocking If supported by hardware and enabled, outbound AtomicOp

Requests through the Egress Ports are blocked. Default is Disabled.

IDO Request Enable If supported by hardware and enabled, allows you to set the number

of ID-Based Ordering (IDO) bit (Attribute[2]) requests to be initiated.

Default is Disabled.

IDO Completion Enable If supported by hardware and enabled, allows you to enable ID-

Based Ordering (IDO) Completion bit. Default is Disabled.

LTR Mechanism Enable If supported by hardware and enabled, allows you to enable the

Latency Tolerance Reporting (LTR) Mechanism. Default is Disabled.

End-End TLP Prefix Blocking If supported by hardware and enabled, allows you to block

forwarding of Traffic Light Protocols (TLPs) that contain End-End

TLP Prefixes. Default is Disabled.

PCI Express GEN2 Link Register Settings

Target Link Speed If supported by hardware and you select Force to X.X (2.5, 5.0, 9.0,

16.0, or 32.0) GT/s for downstream ports, you set an upper limit on

the link operational speed by restricting the values advertised by the

upstream component in its training sequences. Auto (default) uses

hardware initialized data.

Clock Power Management If supported by hardware and and enabled, the device uses the

CLKREQ# signal for power management of the link clock, with the

protocol defined in the form factor specification. Default is Disabled.

Compliance SOS If supported by hardware and and enabled, forces Link Training and

Status State Machine (LTSSM) to send Sealed Key Protection

(SKP) Ordered Sets between sequences when sending Compliance

Pattern or Modified Compliance Pattern. Default is Disabled.

Hardware Autonomous Width If supported by hardware and and disabled, the hardware cannot

change the link width except for width size reduction to correct an

unstable link operation. Default is Enabled.

Hardware Autonomous Speed If supported by hardware and and disabled, the hardware cannot

change the link speed except for speed rate reduction to correct an

unstable link operation. Default is Enabled.

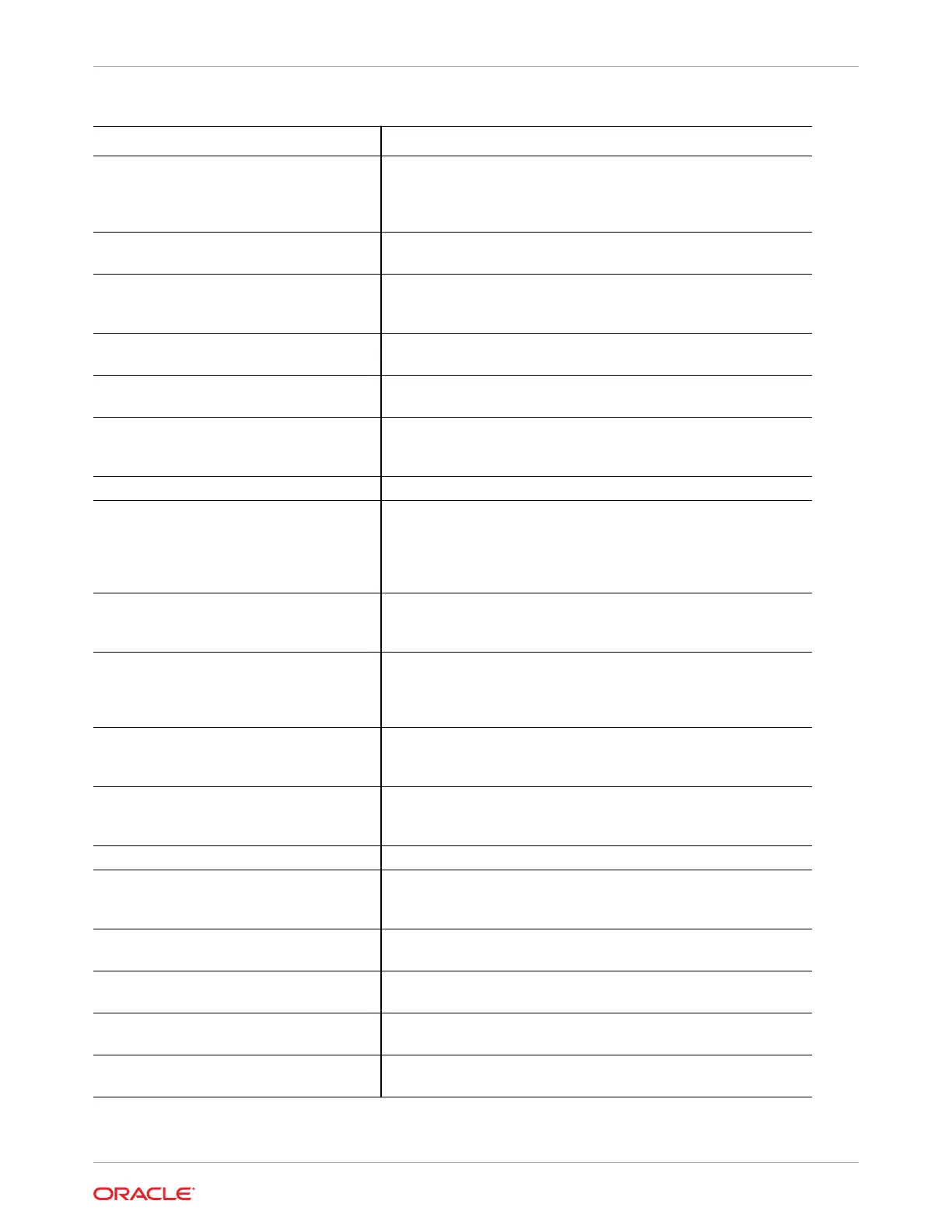

PCI Hot-Plug Settings

BIOS Hot-Plug Support Allows BIOS build in Hot-Plug support, if the operating system does

not support PCI Express and Standard Hot-Plug Controller (SHPC)

hot-plug natively. Default is Enabled.

PCI Buses Padding Pads the PCI buses behind the bridge for hot-plug. Select 1-5.

Default is 1.

I/O Resources Padding Pads the I/O resources behind the bridge for hot-plug. Select 4 K, 8

K, 16 K, or 32 K. Default is 4K.

MMIO 32 Bit Resources Padding Pads the PCI Memory-Mapped IO (MMIO) 32-bit resources behind

the bridge for hot-plug. Default is 16 M.

PFMMIO 32 Bit Resources Padding Pads the PFMMIO 32-bit prefetchable resources behind the bridge

for hot-plug. Default is 16 M.

Appendix F

Advanced Menu

F-9

Loading...

Loading...