System variables

108580_en_02 PHOENIX CONTACT 181 / 272

DBG Non-safe debug mode of the iSPNS 3000

This bit is set when the iSPNS 3000 is in one of the two DEBUG states (DEBUG RUN or

DEBUG STOP/SINGLE). This bit is not set in the SAFE STOP and SAFE RUN states.

Bits 7 and 10

WARN The set WARN (WARNING) bit indicates a group warning message of the iSPNS 3000.

Bit 12

EST The EST (error stack) bit indicates that diagnostic and error messages for the safe

iSPNS 3000 operating system are present. These messages are shown on the display and

can be read and evaluated by PLCnext Engineer.

This bit is always set if there is at least one entry in the error memory of the safe operating

system. As soon as the error memory has been read and emptied via PLCnext Engineer,

this bit is automatically reset to zero.

Bit 14

POST POWER-ON SELFTEST

This bit is set for the duration of the comprehensive power-on selftest of the iSPNS 3000. It

is reset once the power-on selftest is complete.

Bit 15

FS Failure state

This bit is set as soon as an error has been detected, which sets the iSPNS 3000 to the fail-

ure state. The corresponding additional error code is included in this state in the diagnostic

parameter registers of the iSPNS 3000 (SPNS.DIAG.PARAM_REG and

SPNS.DIAG.PARAM_2_REG).

Res. Reserved

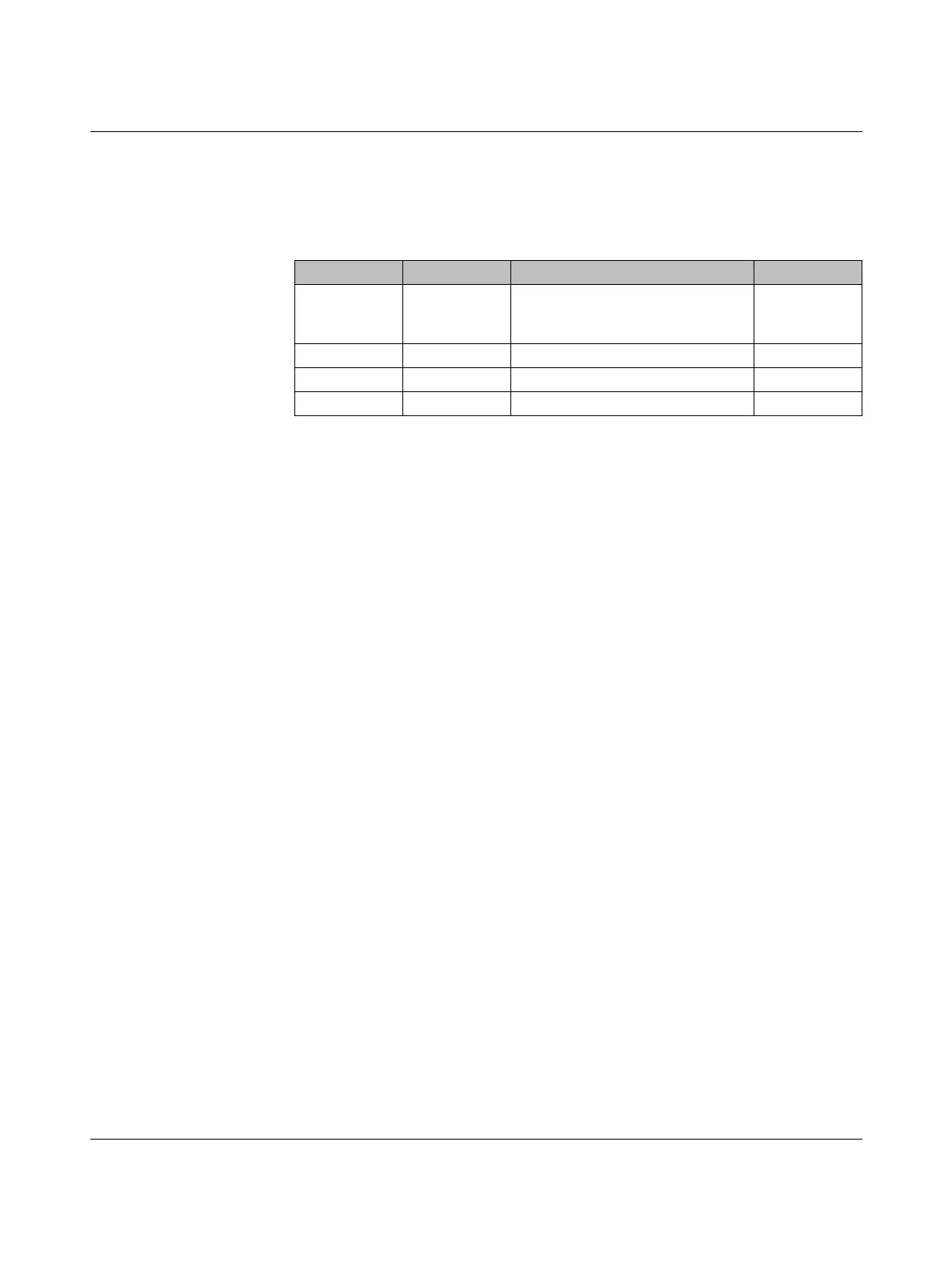

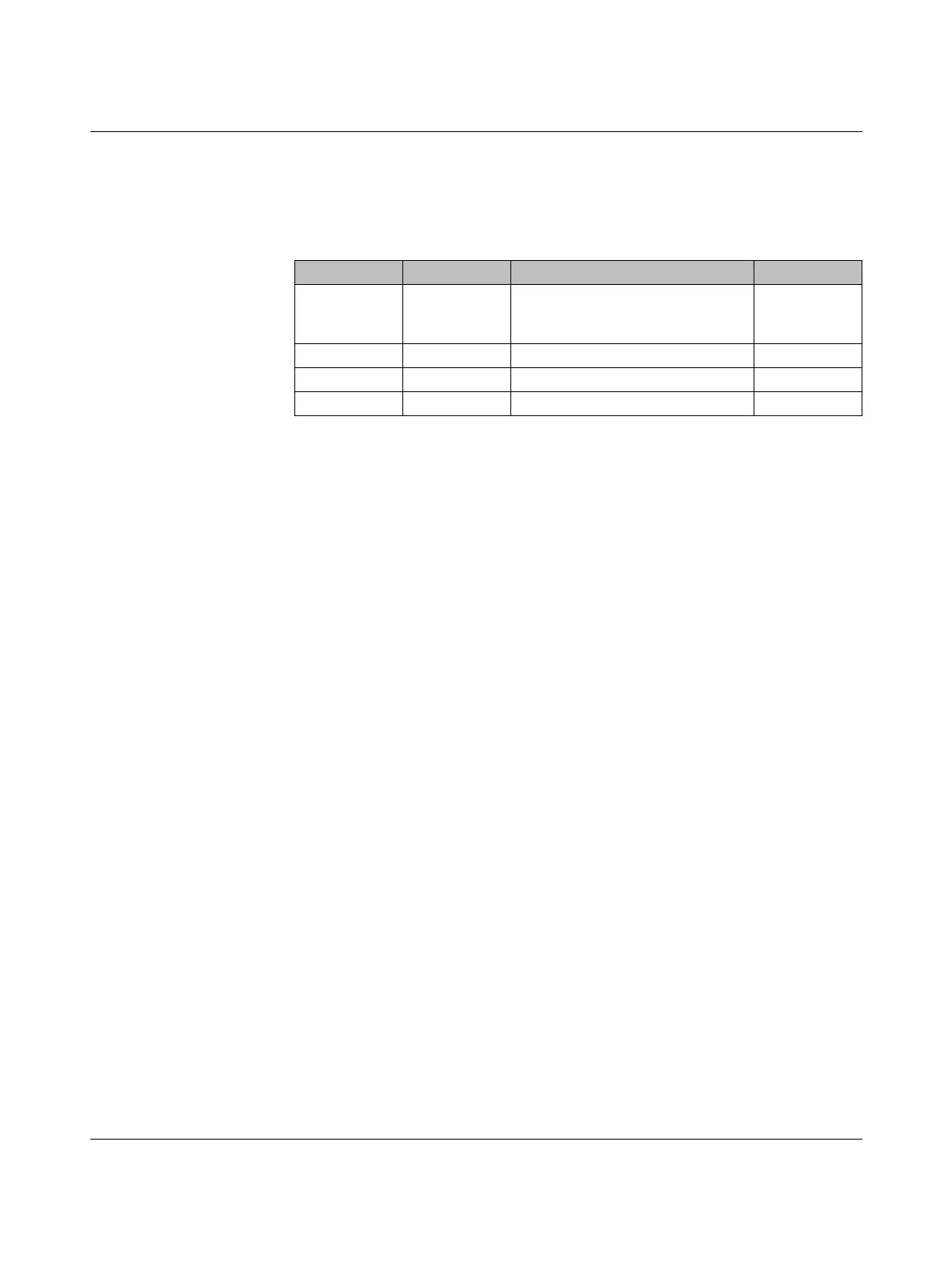

Table 8-4 Contents of bits 5 and 6 and corresponding LED indicators

1

1

Indicated by means of the virtual FS LEDs in the “Safety PLC” tile of the display

RUN bit DBG bit State FS LED

00

Startup sequence (bits 0 to 4)

or

SAFE STOP

Flashing

Off

0 1 DEBUG STOP/SINGLE Flashing

10 SAFE RUN Off

1 1 DEBUG RUN Flashing

Loading...

Loading...