150 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 3: Advanced SelectIO Logic Resources

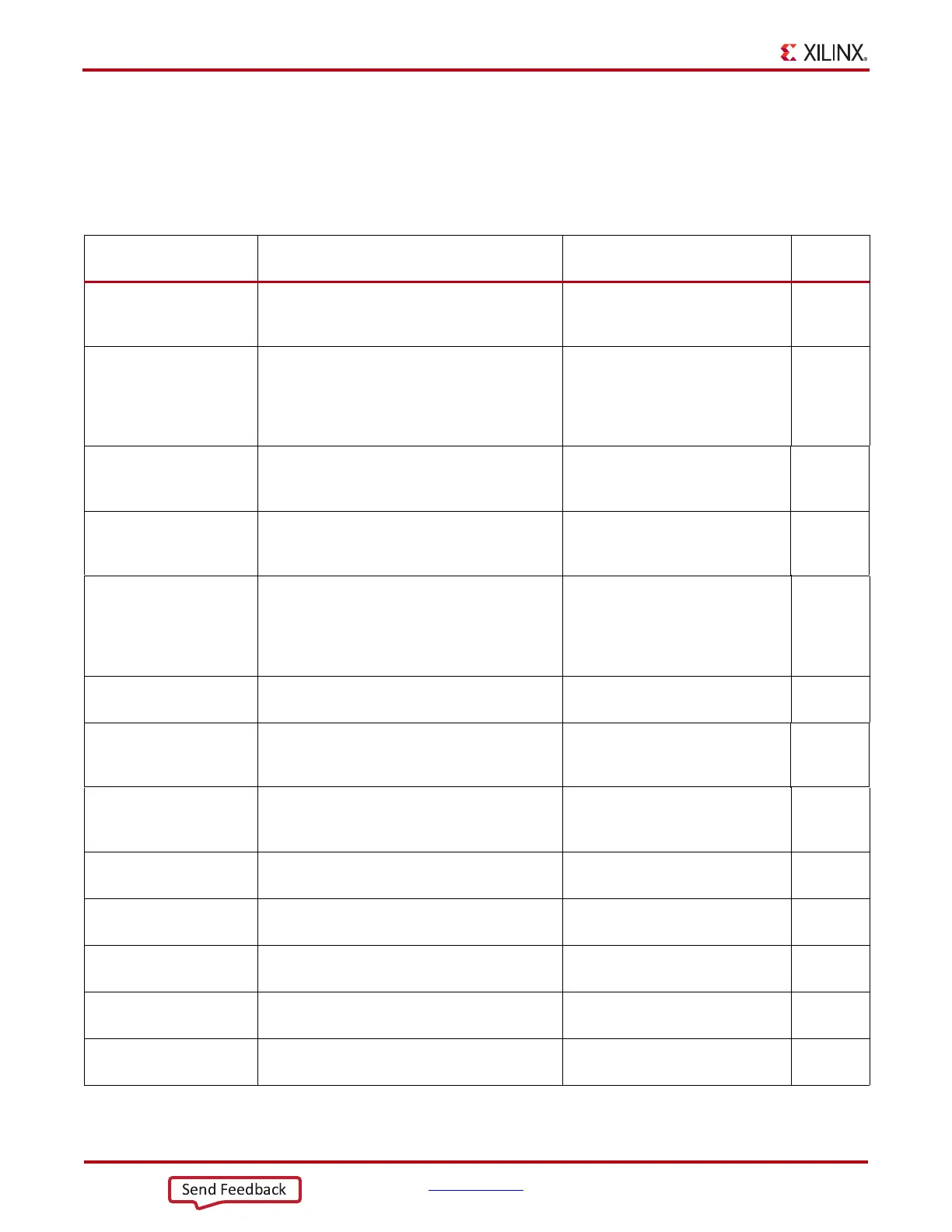

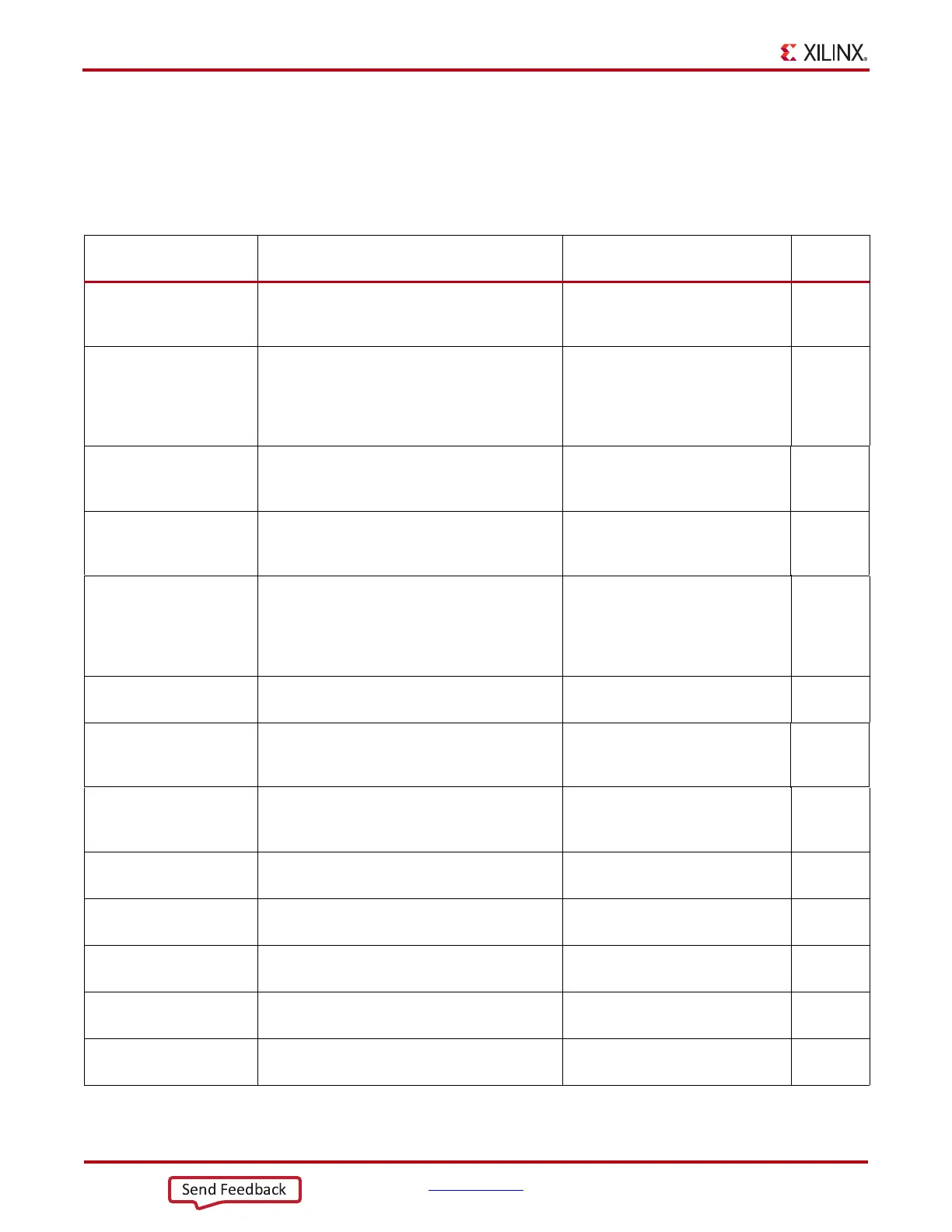

ISERDESE2 Attributes

Table 3-2 summarizes all the applicable ISERDESE2 attributes. A detailed description of

each attribute follows the table. For more information on applying these attributes in UCF,

VHDL, or Verilog code, refer to the Xilinx ISE Software Manual.

Table 3-2: ISERDESE2 Attributes

Attribute Name Description Value

Default

Value

DATA_RATE Enables incoming data stream to be

processed as SDR or DDR data. See

DATA_RATE Attribute.

String: SDR or DDR DDR

DATA_WIDTH Defines the width of the serial-to-parallel

converter. The legal value depends on the

DATA_RATE attribute (SDR or DDR). See

DATA_WIDTH Attribute.

Integer: 2, 3, 4, 5, 6, 7, 8, 10 or 14.

If DATA_RATE = DDR, value is

limited to 4, 6, 8, 10, or 14.

If DATA_RATE = SDR, value is

limited to 2, 3, 4, 5, 6, 7, or 8.

4

DYN_CLKDIV_INV_EN Enables DYNCLKDIVSEL inversion when

TRUE and disables HDL inversions on

CLKDIV pin. See Dynamic Clock Inversions.

Boolean: TRUE or FALSE FALSE

DYN_CLK_INV_EN Enables DYNCLKSEL inversion when TRUE

and disables HDL inversions on CLK and

CLKB pins. See Dynamic Clock Inversions.

Boolean: TRUE or FALSE FALSE

INTERFACE_TYPE Chooses the ISERDESE2 use model. See

INTERFACE_TYPE Attribute.

String: MEMORY,

MEMORY_DDR3,

MEMORY_QDR,

OVERSAMPLE, or

NETWORKING

MEMORY

NUM_CE Defines the number of clock enables. See

NUM_CE Attribute.

Integer: 1 or 2 2

OFB_USED Enables the path from the OLOGICE2/3,

OSERDESE2 OFB pin to the ISERDESE2 OFB

pin. Disables the use of the D input pin.

Boolean: TRUE or FALSE FALSE

SERDES_MODE Defines whether the ISERDESE2 module is a

master or slave when using width expansion.

See SERDES_MODE Attribute.

String: MASTER or SLAVE MASTER

INIT_Q1 Sets the initial value for the first sample

register.

Binary: 0 or 1 0

INIT_Q2 Sets the initial value for the second sample

register.

Binary: 0 or 1 0

INIT_Q3 Sets the initial value for the third sample

register.

Binary: 0 or 1 0

INIT_Q4 Sets the initial value for the fourth sample

register.

Binary: 0 or 1 0

SRVAL_Q1 Sets the value after reset of the first sample

register.

Binary: 0 or 1 1

Loading...

Loading...