106 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 2: SelectIO Logic Resources

ILOGIC Resources

The ILOGIC block is located next to the I/O block (IOB). The ILOGIC block contains the

synchronous elements for capturing data as it comes into the FPGA through the IOB. The

possibilities for ILOGIC configuration in 7 series devices are the ILOGICE2 (HP I/O

banks) and ILOGICE3 (HR I/O banks). Although always described as ILOGIC in this

guide, unless explicitly delineated, ILOGICE2 and ILOGICE3 are functionally identical

and so are their ports. The only differences between ILOGICE2 and ILOGICE3 are:

• ILOGICE3 is located in the HR banks and has a zero hold delay element (ZHOLD).

• ILOGICE2 is located in the HP banks and does not have a ZHOLD element.

These differences are shown in Figure 2-3 and Figure 2-4. The ZHOLD delay at the D-input

of the input/output interconnect (IOI) storage element eliminates any pad-to-pad hold

time requirement. The ZHOLD delay is automatically matched to the internal

clock-distribution delay, and when used, assures that the pad-to-pad hold time is zero. The

ILOGIC block supports an optional static uncompensated zero hold (ZHOLD) delay line

on inputs to compensate for clock insertion delay. The ZHOLD feature is optimized to

compensate for clock insertion delays when the clocking path is directly sourced from a

BUFG/BUFGCE that is sourced in the same bank or on an adjacent bank. ZHOLD is

enabled by default unless the clock source is an MMCM or PLL, or unless the IOBDELAY

attribute is set in the Xilinx design constraints (XDC).

Important:

ZHOLD might not be appropriate for all applications, so consult the timing report to

verify the impact to a specific clocking scheme.

ILOGICE2 and ILOGICE3 are not primitives in the sense that they cannot be instantiated.

They contain user-instantiated elements such as an input flip-flop (IFD) or an input DDR

element (IDDR) after place and route.

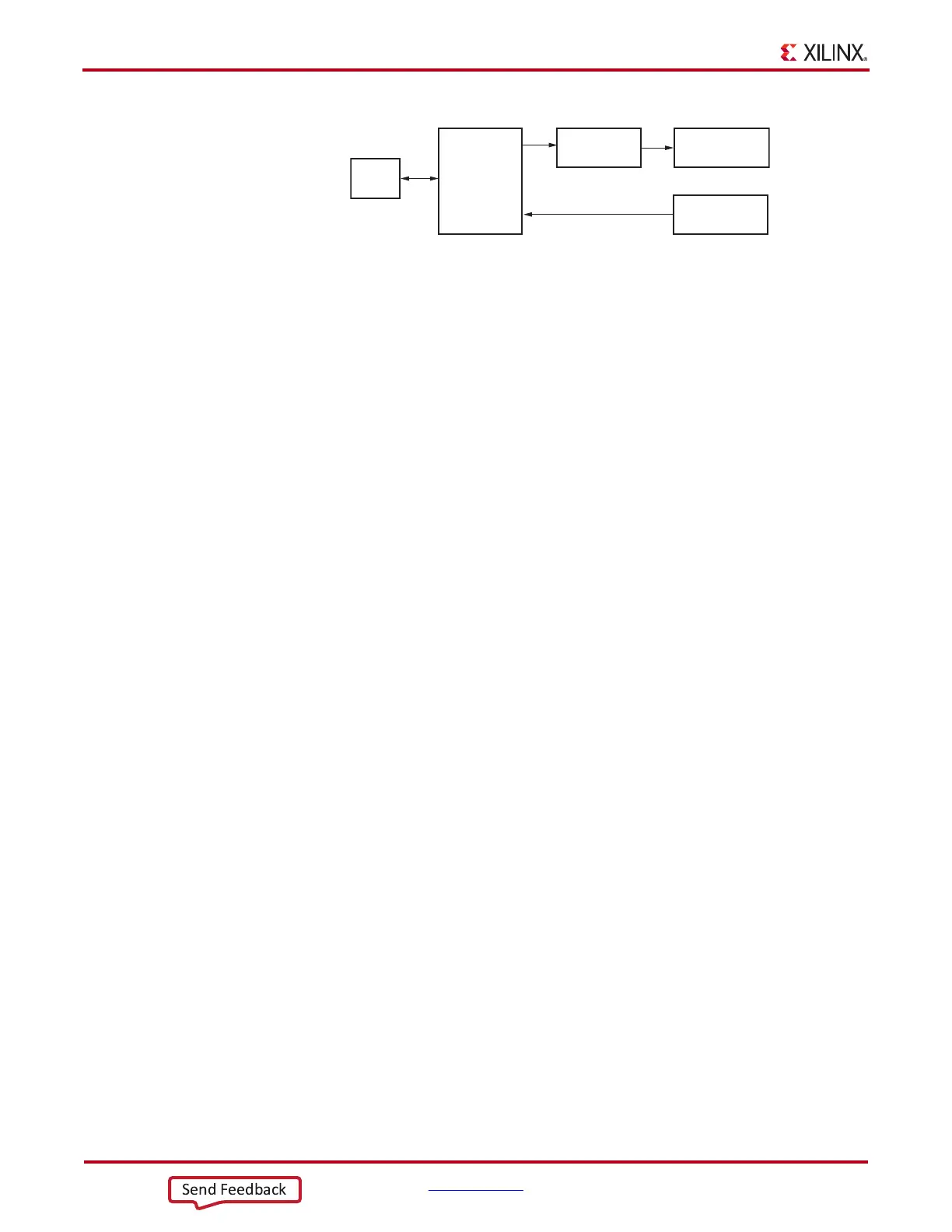

X-Ref Target - Figure 2-2

Figure 2-2: 7 Series FPGA HR Bank I/O Tile

UG471_c1_02_012211

IDELAYE2

IOB

ILOGICE3/

ISERDESE2

OLOGICE3/

OSERDESE2

PA D

Loading...

Loading...