36 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 1: SelectIO Resources

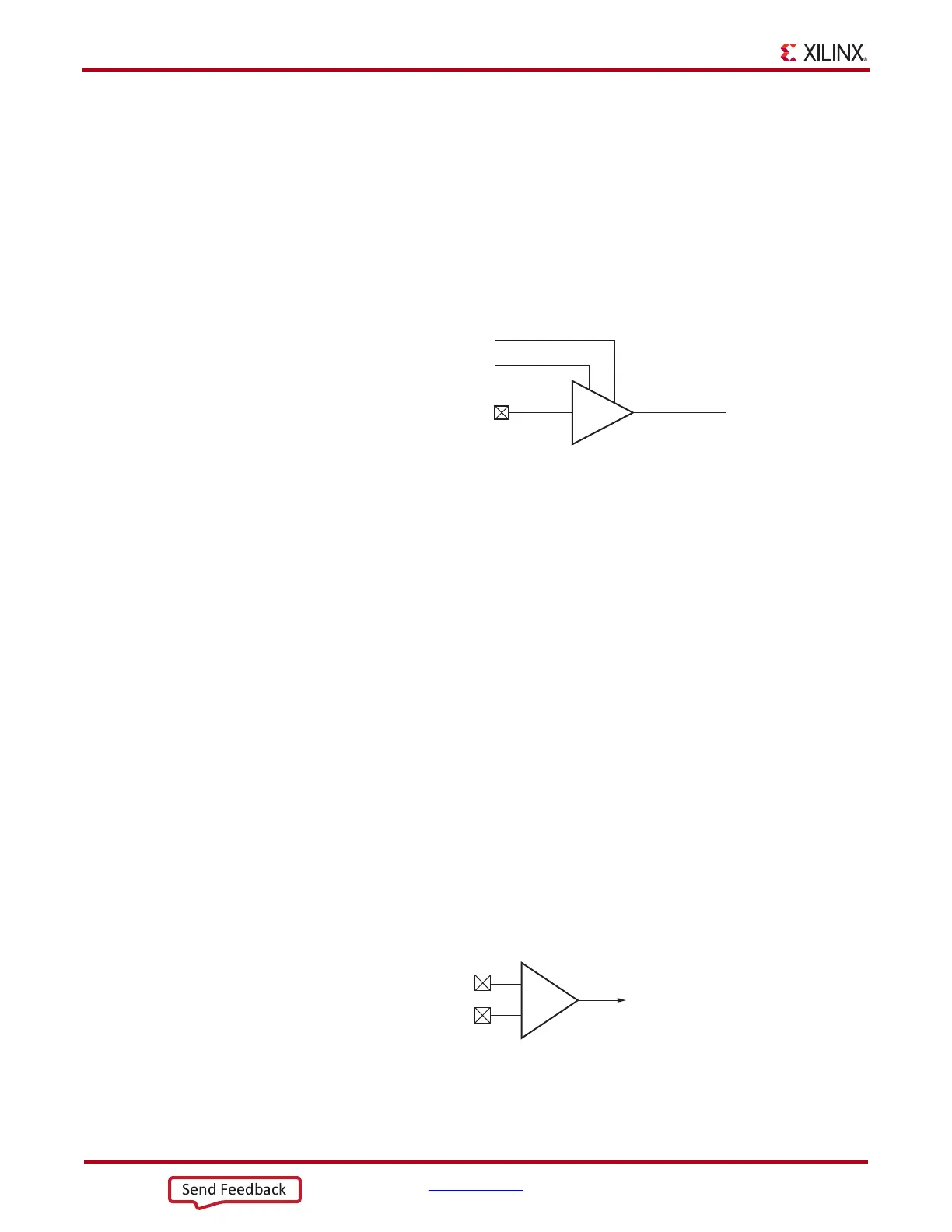

IBUF_INTERMDISABLE

The IBUF_INTERMDISABLE primitive shown in Figure 1-17 is available in the HR I/O

banks and is similar to the IBUF_IBUFDISABLE primitive in that it has a IBUFDISABLE

port that can be used to disable the input buffer during periods that the buffer is not being

used. The IBUF_INTERMDISABLE primitive also has an INTERMDISABLE port that can

be used to disable the optional uncalibrated split-termination feature. See Uncalibrated

Split Termination in High-Range I/O Banks (IN_TERM) for more details about this

feature.

The IBUF_INTERMDISABLE primitive can disable the input buffer and force the O output

to the fabric to a logic High when the USE_IBUFDISABLE attribute is set to TRUE and the

IBUFDISABLE signal is asserted High. If USE_IBUFDISABLE is set to FALSE, this input is

ignored and should be tied to ground. If the I/O is using the optional uncalibrated

split-termination feature (IN_TERM), those termination legs are disabled whenever the

driver is active (T is low). The IBUF_INTERMDISABLE primitive further allows the

termination legs to be disabled whenever the INTERMDISABLE signal is asserted High.

These features can be combined to reduce power whenever the input is idle. Input buffers

that use the VREF power rail (such as SSTL and HSTL) benefit the most from the

IBUFDISABLE signal being set to TRUE because they tend to have higher static power

consumption than the non-VREF standards such as LVCMOS and LVTTL.

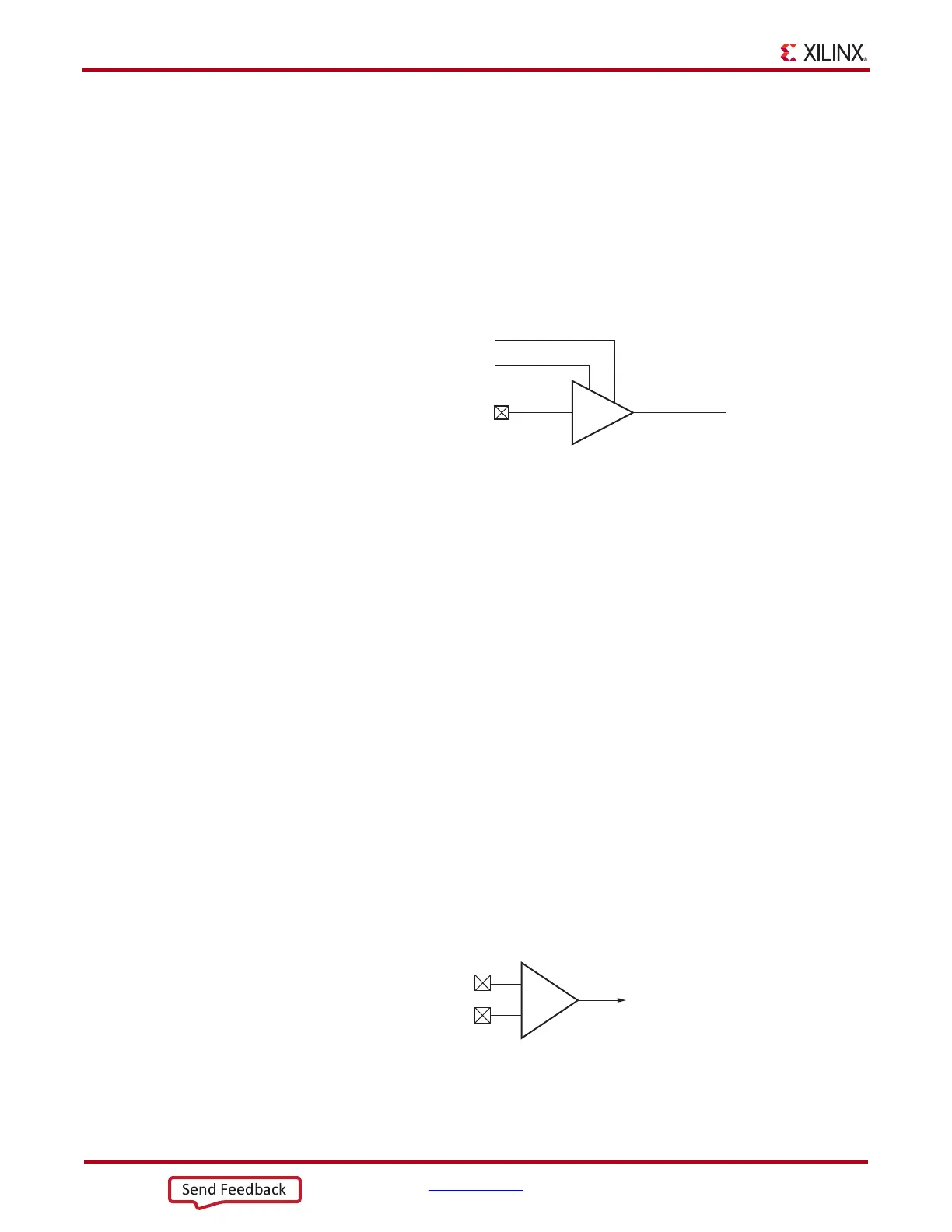

IBUFDS and IBUFGDS

The usage and rules corresponding to the differential primitives are similar to the

single-ended SelectIO primitives. Differential SelectIO primitives have two pins to and

from the device pads to show the P and N channel pins in a differential pair. N channel

pins have a B suffix. The IBUFDS and IBUFGDS primitives are the same, IBUFGDS is used

when an differential input buffer is used as a clock input.

Figure 1-18 shows the differential input buffer primitive.

X-Ref Target - Figure 1-1 7

Figure 1-17: Input Buffer With Input Buffer Disable and IN_TERM Disable

(IBUF_INTERMDISABLE)

IBUF_INTERMDISABLE

IBUFDISABLE

INTERMDISABLE

IO

UG471_c1_64_041412

X-Ref Target - Figure 1-1 8

Figure 1-18: Differential Input Buffer Primitives (IBUFDS/IBUFGDS)

ug471_c1_21_041112

+

–

I

IB

O

IBUFDS/IBUFGDS

Inputs from

device pads

Output to

FPGA

Loading...

Loading...