96 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 1: SelectIO Resources

BLVDS (Bus LVDS)

Since LVDS is intended for point-to-point applications, BLVDS is not an EIA/TIA standard

implementation and requires careful adaptation of I/O and PCB layout design rules. The

primitive supplied in the software library for bidirectional LVDS does not use the 7 series

FPGA LVDS current-mode driver, instead, it uses complementary single-ended differential

drivers. Therefore, source termination is required. BLVDS is only available in HR I/O

banks and requires a V

CCO

voltage level of 2.5V. The IOSTANDARD is called BLVDS_25.

Table 1-54 summarizes all the possible BLVDS I/O standards.

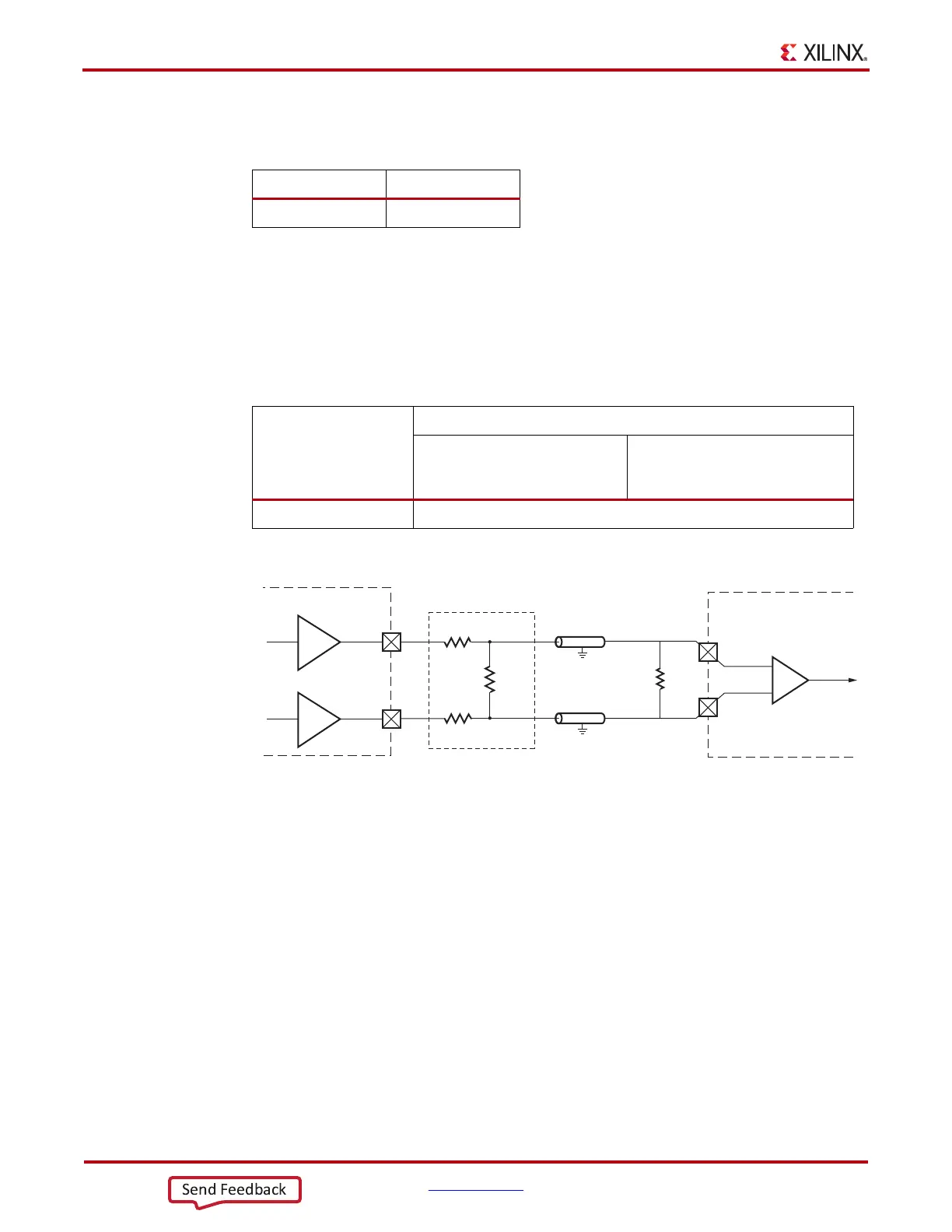

Figure 1-73 shows the BLVDS transmitter termination.

Table 1-53: Available I/O Bank Type

HR HP

Available N/A

Table 1-54: Allowed Attributes of the BLVDS I/O Standard

Attributes

Primitives

IBUFDS, IBUFGDS,

IBUFDS_DIFF_OUT, or

IBUFGDS_DIFF_OUT

OBUFDS, OBUFTDS, IOBUFDS,

or IOBUFDS_DIFF_OUT

IOSTANDARD

BLVDS_25

X-Ref Target - Figure 1-7 3

Figure 1-73: BLVDS Transmitter Termination

ug471_c1_62_011811

Z

0

= 50Ω

Z

0

= 50Ω

R

DIV

140Ω

R

DIFF

= 100Ω

R

S

165Ω

R

S

165Ω

IN

INX

Data in

-

+

BLVDS_25

IOB

BLVDS_25

BLVDS_25

IOB

Loading...

Loading...