66 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 1: SelectIO Resources

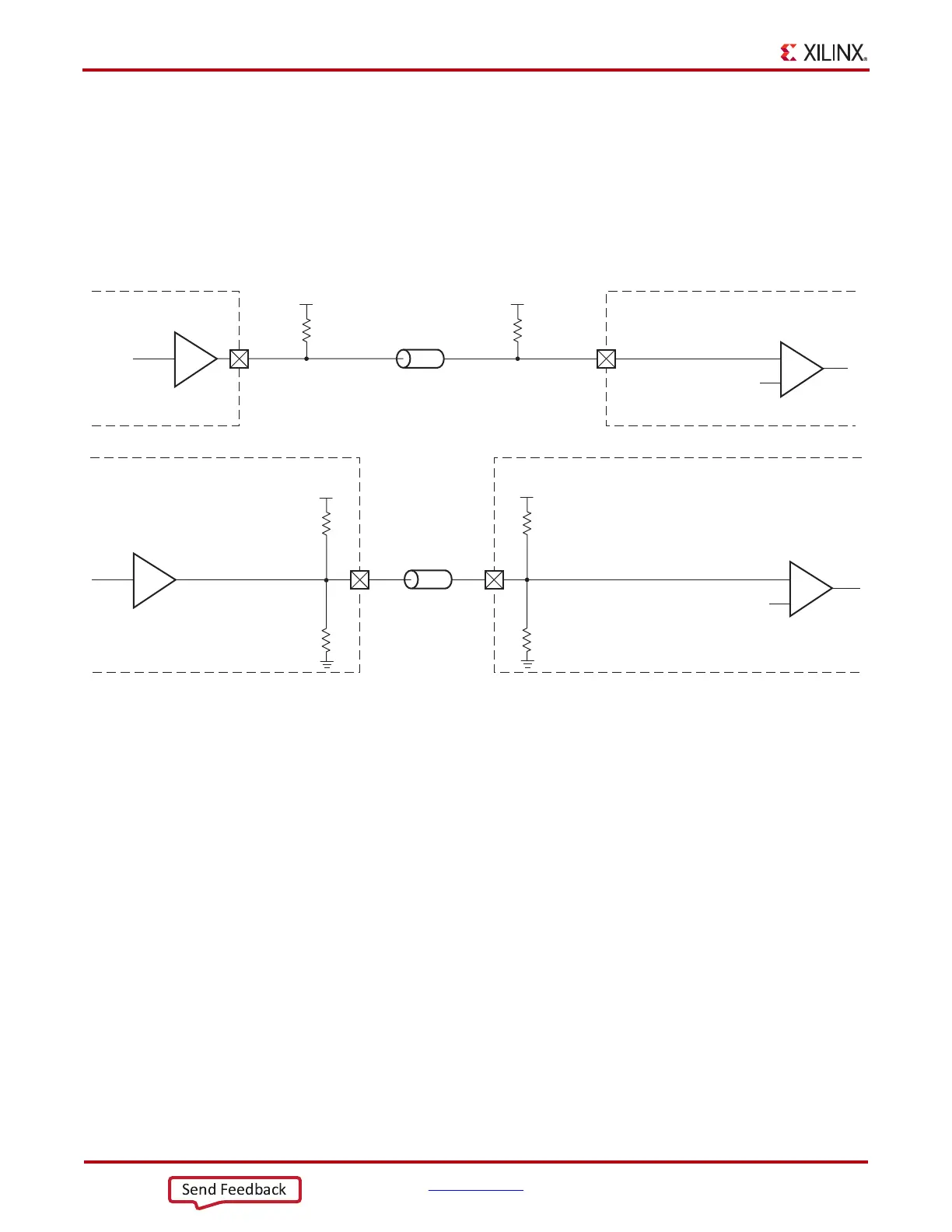

HSTL Class II

Figure 1-49 shows a sample circuit illustrating a termination technique for HSTL class-II

(1.5V or 1.8V) with unidirectional termination. In a specific circuit, all drivers and receivers

must be at the same voltage level (either 1.5V or 1.8V); they are not interchangeable. Only

HP I/O banks support the DCI standards. The internal split-termination resistors are

always present, independent of whether the drivers are 3-stated.

X-Ref Target - Figure 1-49

Figure 1-49: HSTL Class II (1.5V or 1.8V) Unidirectional Termination

Z

0

IOB

IOB

HSTL_II

HSTL_II_18

HSTL_II

HSTL_II_18

ug471_c1_39_121214

V

TT

= 0.75V for HSTL_II

0.9V for HSTL_II_18

V

TT

= 0.75V for HSTL_II

0.9V for HSTL_II_18

R

P

= Z

0

= 50Ω

R

P

= Z

0

= 50Ω

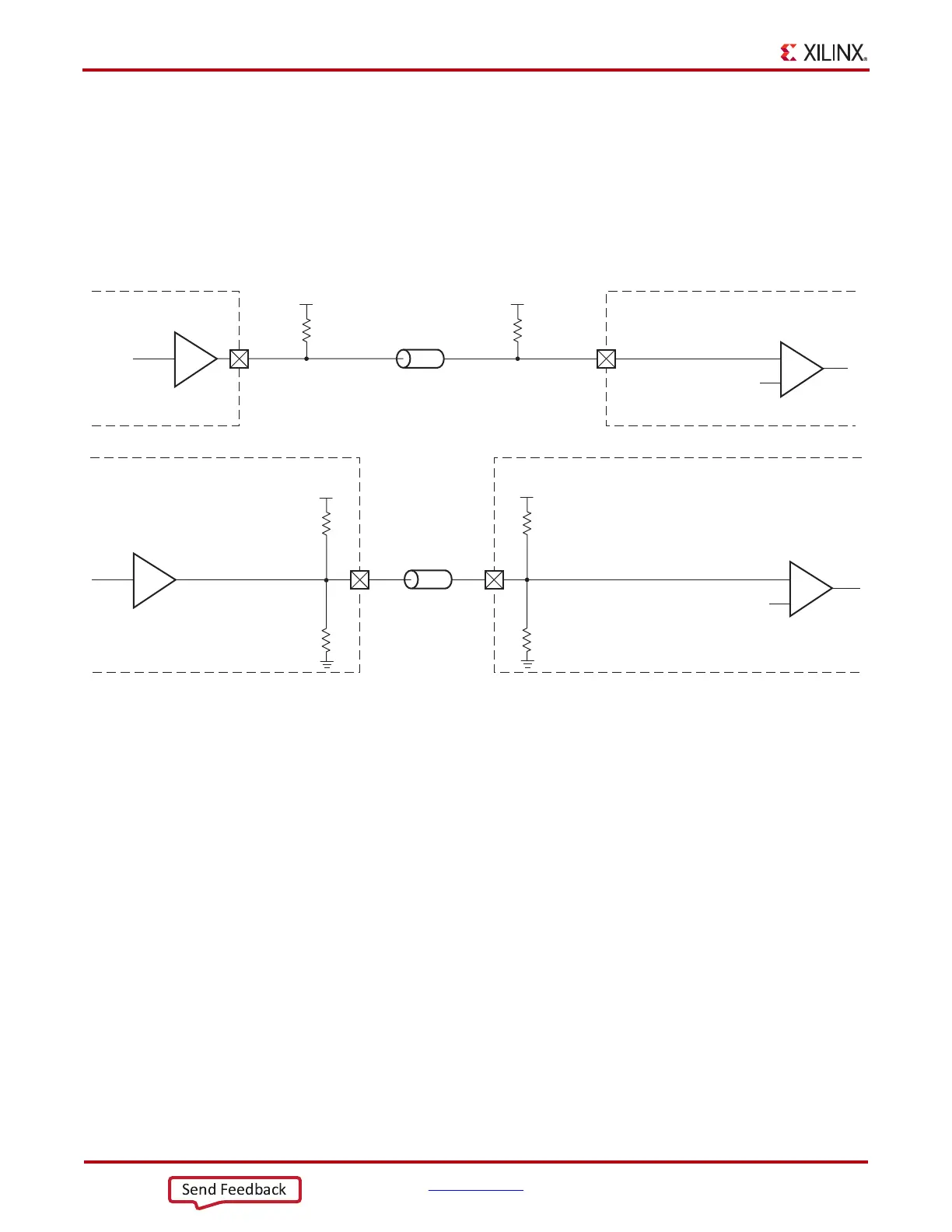

Z

0

IOB

IOB

HSTL_II_DCI

HSTL_II_DCI_!8

HSTL_II_DCI

HSTL_II_DCI_!8

V

CCO

= 1.5V for HSTL_II_DCI

1.8V for HSTL_II_DCI_18

V

CCO

= 1.5V for HSTL_II_DCI

1.8V for HSTL_II_DCI_18

R

VRN

= 2Z

0

= 100Ω

R

VRP

= 2Z

0

= 100Ω

V

REF

=

0.75V for HSTL_II

0.9V for HSTL_II_18

V

REF

=

0.75V for HSTL_II_DCI

0.9V for HSTL_II_DCI_18

+

–

+

–

External Termination

DCI

R

VRN

= 2Z

0

= 100Ω

R

VRP

= 2Z

0

= 100Ω

Loading...

Loading...