7 Series FPGAs SelectIO Resources User Guide www.xilinx.com 111

UG471 (v1.10) May 8, 2018

ILOGIC Resources

Input DDR Resources (IDDR)

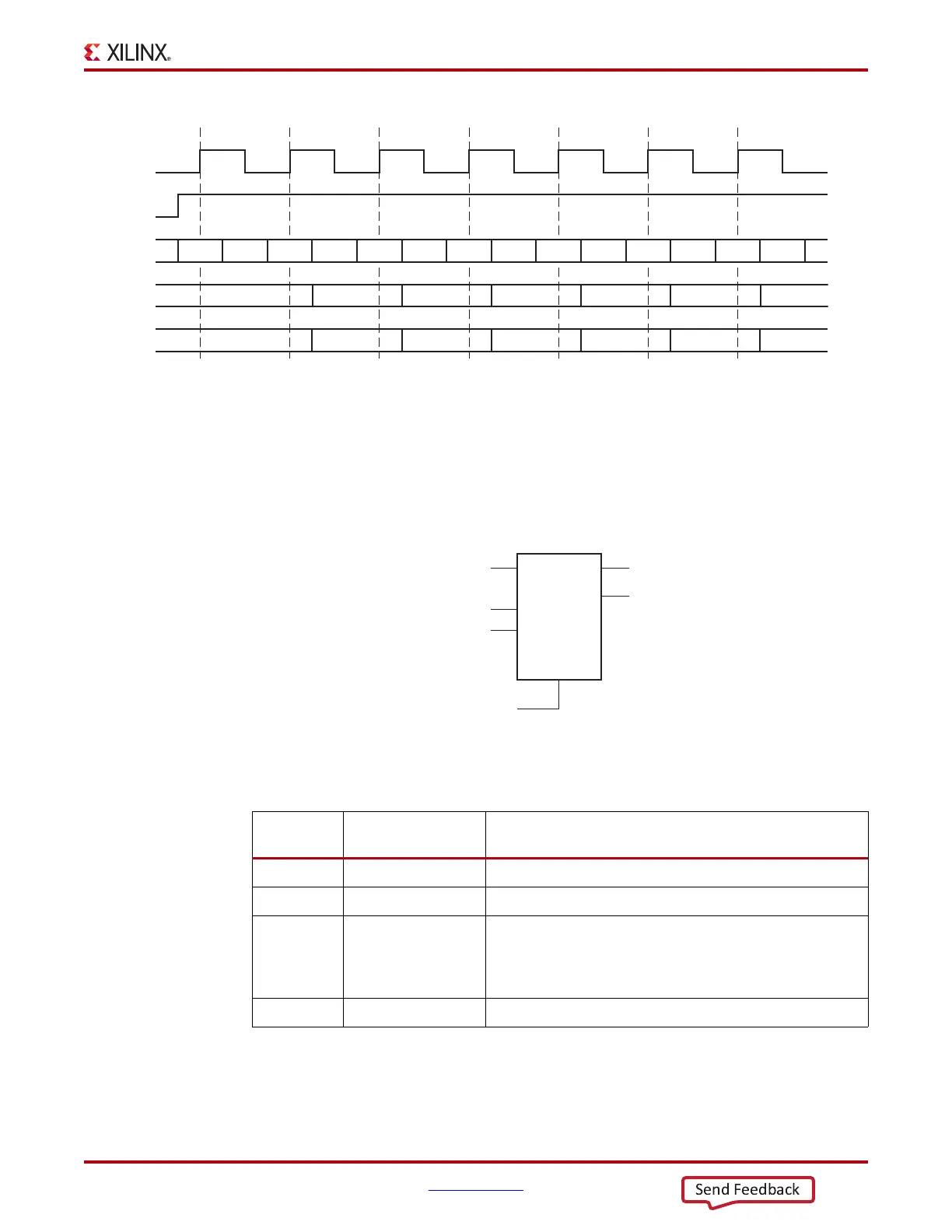

Figure 2-8 shows the block diagram of the IDDR primitive. Set and Reset are not supported

at the same time. Table 2-1 lists the IDDR port signals. Table 2-2 describes the various

attributes available and default values for the IDDR primitive.

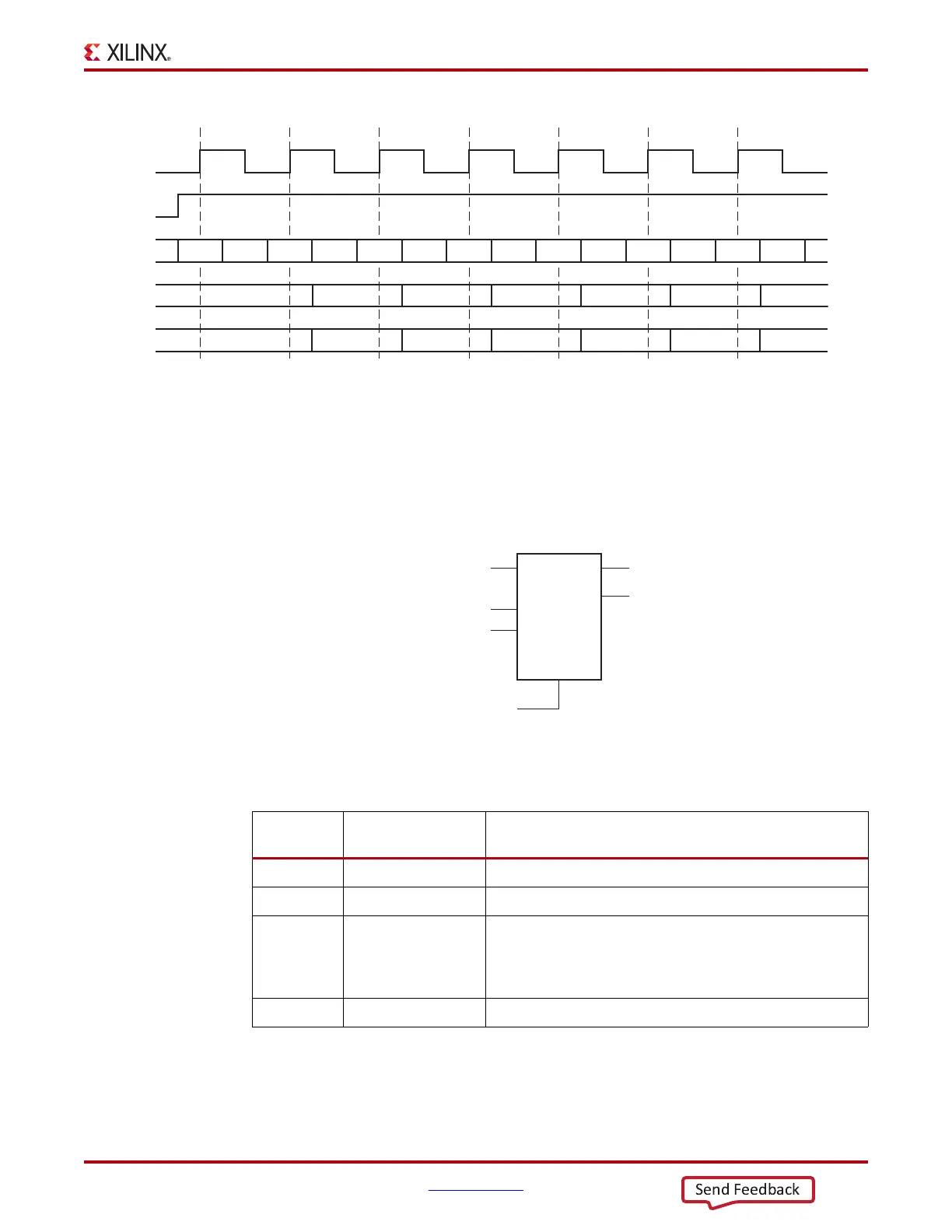

X-Ref Target - Figure 2-7

Figure 2-7: Input DDR Timing in SAME_EDGE_PIPELINED Mode

ug471_c2_05_090810

C

CE

D

Q1

Q2

D0A D1A D2A

D0A D2A D4A D6A D8A D10A

D1A D3A D5A D7A D9A D11A

D3A

D4A D5A D6A D7A D8A D9A D10A D11A D12A D13A

X-Ref Target - Figure 2-8

Figure 2-8: IDDR Primitive Block Diagram

Table 2-1: IDDR Port Signals

Port

Name

Function Description

Q1 and Q2 Data outputs IDDR register outputs.

C Clock input port The C pin represents the clock input pin.

CE Clock enable port The enable pin affects the loading of data into the DDR

flip-flop. When Low, clock transitions are ignored and

new data is not loaded into the DDR flip-flop. CE must be

High to load new data into the DDR flip-flop.

D Data input (DDR) IDDR register input from IOB.

ug471_c2_06_061215

C

CE

D

S/R

Q1

Q2

IDDR

Loading...

Loading...