7 Series FPGAs SelectIO Resources User Guide www.xilinx.com 137

UG471 (v1.10) May 8, 2018

Output Delay Resources (ODELAY)—Not Available in HR Banks

ODELAY Attributes

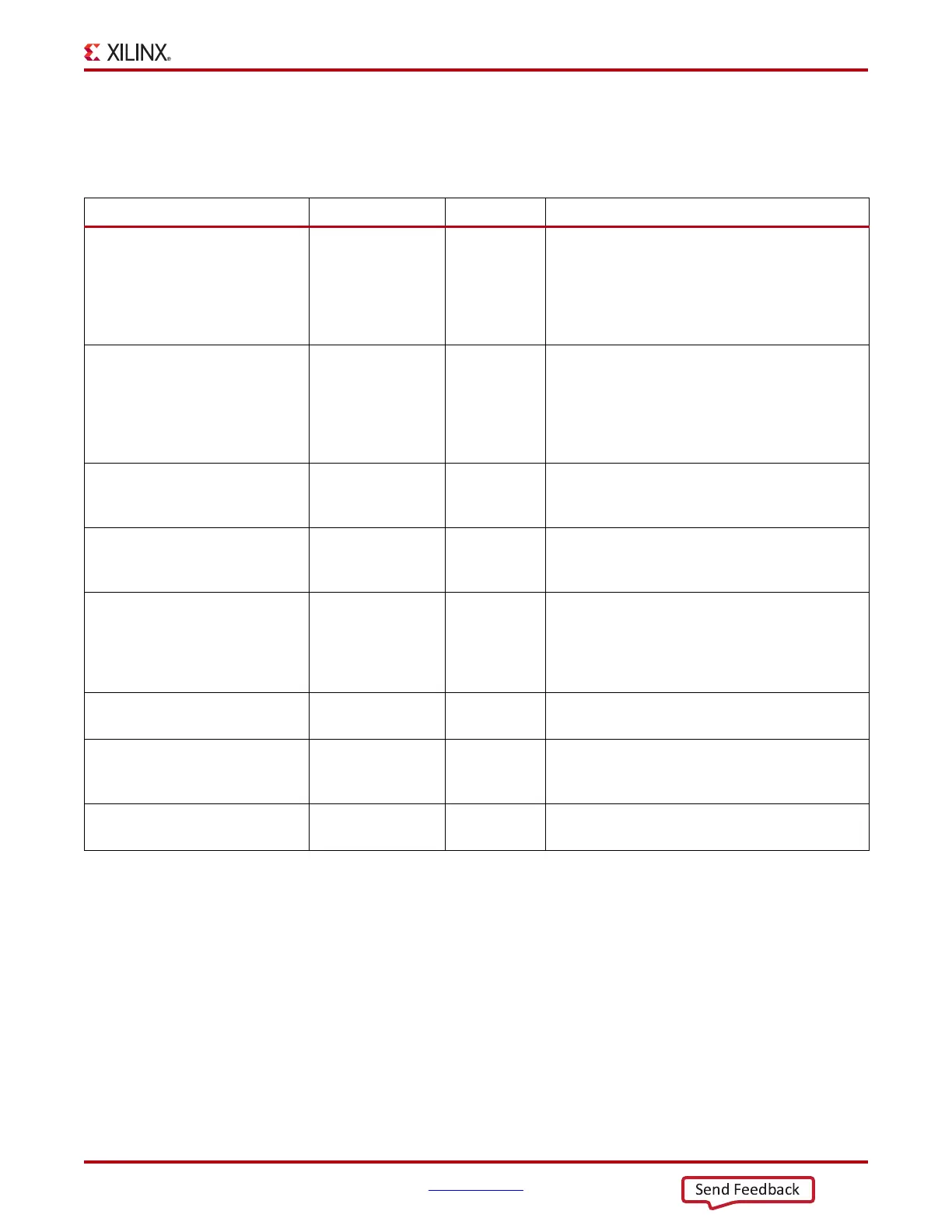

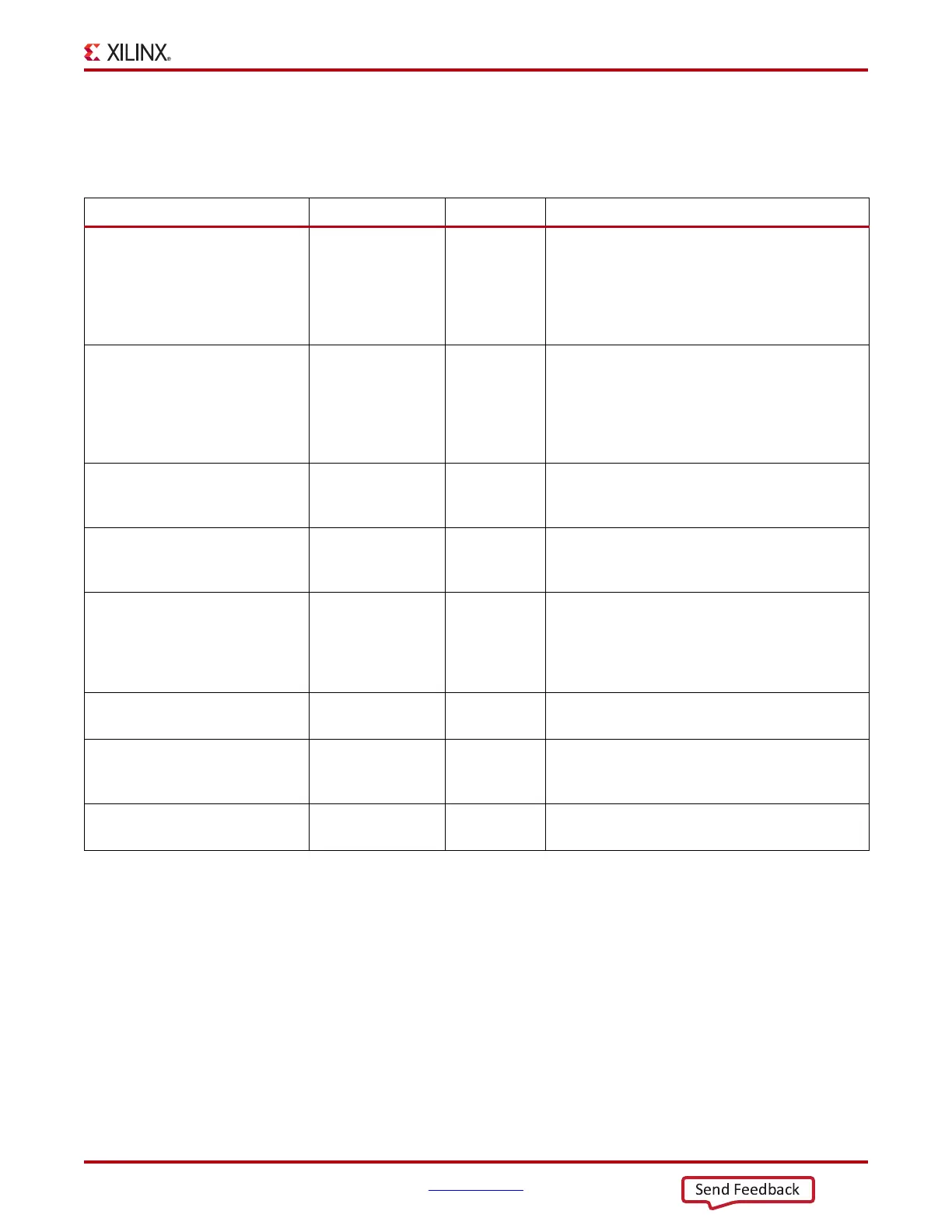

Table 2-14 summarizes the ODELAY attributes.

ODELAY_TYPE Attribute

When set to FIXED, the tap-delay value is fixed at the number of taps determined by the

ODELAY_VALUE attribute setting. This value is preset and cannot be changed after

configuration.

When set to VARIABLE, the variable tap delay is selected. The tap delay can be

incremented by setting CE = 1 and INC = 1, or decremented by CE = 1 and INC = 0. The

increment/decrement operation is synchronous to C.

When set to VAR_LOAD or VAR_LOAD_PIPE, the variable tap delay can be changed and

dynamically loaded. The tap delay can be incremented by setting CE = 1 and INC = 1, or

decremented by CE = 1 and INC = 0. The increment/decrement operation is synchronous

to C. The LD pin in VAR_LOAD mode loads the value presented on CNTVALUEIN. This

Table 2-14: ODELAY Attribute Summary

Attribute Value Default Value Description

ODELAY_TYPE String: FIXED,

VARIABLE,

VAR_LOAD, or

VAR_LOAD_PIPE

FIXED Sets the type of tap delay line. FIXED delay sets

a static delay value. VAR_LOAD dynamically

loads tap values. VARIABLE delay dynamically

adjusts the delay value. VAR_LOAD_PIPE is

similar to VAR_LOAD mode with the ability to

store the CNTVALUEIN value for future use.

ODELAY_VALUE Integer: 0 to 31 0 Specifies the fixed number of delay taps in fixed

mode or the initial starting number of taps in

VARIABLE mode (output path). When

ODELAY_TYPE is set to VAR_LOAD or

VAR_LOAD_PIPE mode, this value is ignored

and assumed to be all zeroes.

HIGH_PERFORMANCE_MODE

Boolean: FALSE or

TRUE

FALSE When TRUE, this attribute reduces the output

jitter. The difference in power consumption is

quantified in the Xilinx Power Estimator tool.

SIGNAL_PATTERN String: DATA,

CLOCK

DATA Causes the timing analyzer to account for the

appropriate amount of delay-chain jitter in the

data or clock path.

REFCLK_FREQUENCY Real: 190–210,

290 to 310, or

390 to 410

200 Sets the tap value (in MHz) used by the timing

analyzer for static timing analysis. The ranges of

290.0 to 310.0 and 390 to 410 are not available in

all speed grades. See the 7 series FPGA data

sheets.

CINVCTRL_SEL Boolean: FALSE or

TRUE

FALSE Enables the CINVCTRL_SEL pin to

dynamically switch the polarity of the C pin.

PIPE_SEL Boolean: FALSE or

TRUE

FALSE Selects pipeline mode. This attribute should

only be set to TRUE when using the

VAR_LOAD_PIPE mode of operation.

DELAY_SRC String: ODATAIN,

CLKIN

ODATAIN Selects source for data input to ODELAY block.

Loading...

Loading...