152 www.xilinx.com 7 Series FPGAs SelectIO Resources User Guide

UG471 (v1.10) May 8, 2018

Chapter 3: Advanced SelectIO Logic Resources

NUM_CE Attribute

The NUM_CE attribute defines the number of clock enables (CE1 and CE2) used. The

possible values are 1 and 2 (default = 2).

SERDES_MODE Attribute

The SERDES_MODE attribute defines whether the ISERDESE2 module is a master or slave

when using width expansion. The possible values are MASTER and SLAVE. The default

value is MASTER. See ISERDESE2 Width Expansion.

ISERDESE2 Clocking Methods

NETWORKING Interface Type

The phase relationship of CLK and CLKDIV is important in the serial-to-parallel

conversion process. CLK and CLKDIV are (ideally) phase-aligned within a tolerance.

There are several clocking arrangements within the FPGA to help the design meet the

phase relationship requirements of CLK and CLKDIV.

The CLK and CLKDIV inputs must be nominally phase-aligned. For example, if CLK and

CLKDIV in Figure 3-6 were inverted by the designer at the ISERDESE2 inputs, then

although the clocking arrangement is an allowed BUFIO/BUFR configuration, the clocks

would still be out of phase. This also prohibits using DYNCLKINVSEL and

DYNCLKDIVINVSEL.

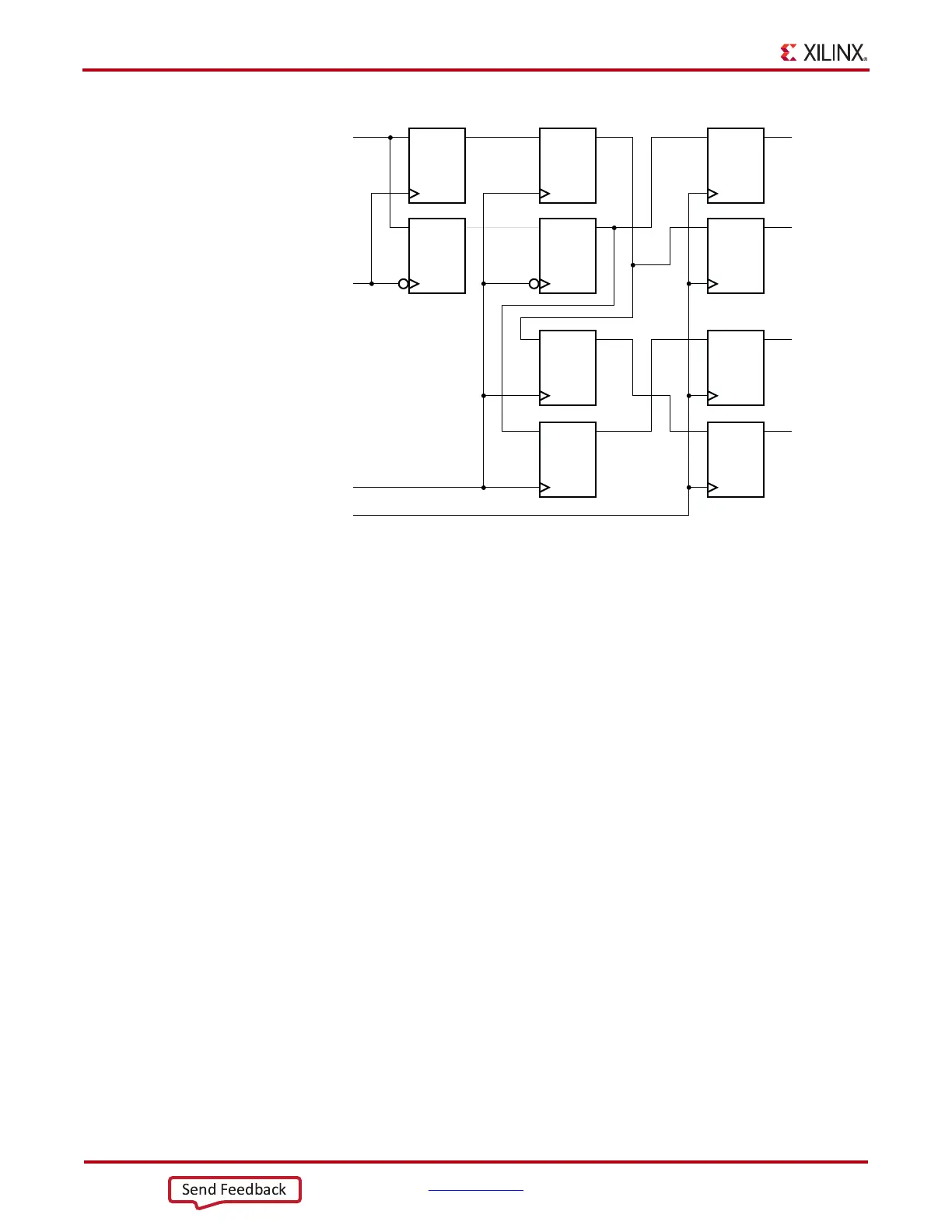

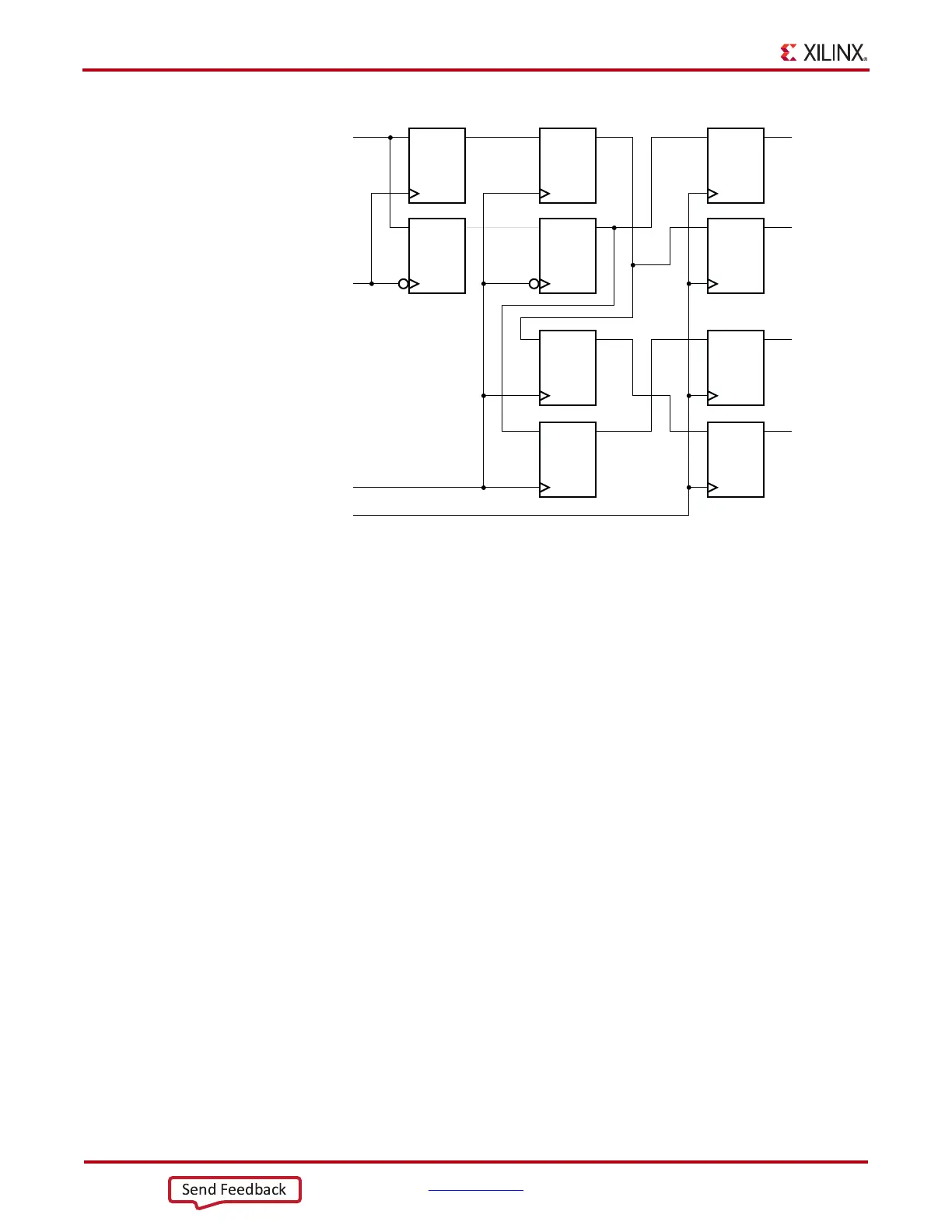

X-Ref Target - Figure 3-5

Figure 3-5: Internal Connections of ISERDESE2 When in MEMORY Mode

Q1D

CLK

ICE

ICE

ICE

ICE

OCLK

CLKDIV

Q2

Q3

Q4

ug471_c3_05_012211

FF0 FF2 FF6

FF1 FF3 FF7

FF4 FF8

FF5 FF9

Loading...

Loading...