136

ABOV Semiconductor Co., Ltd.

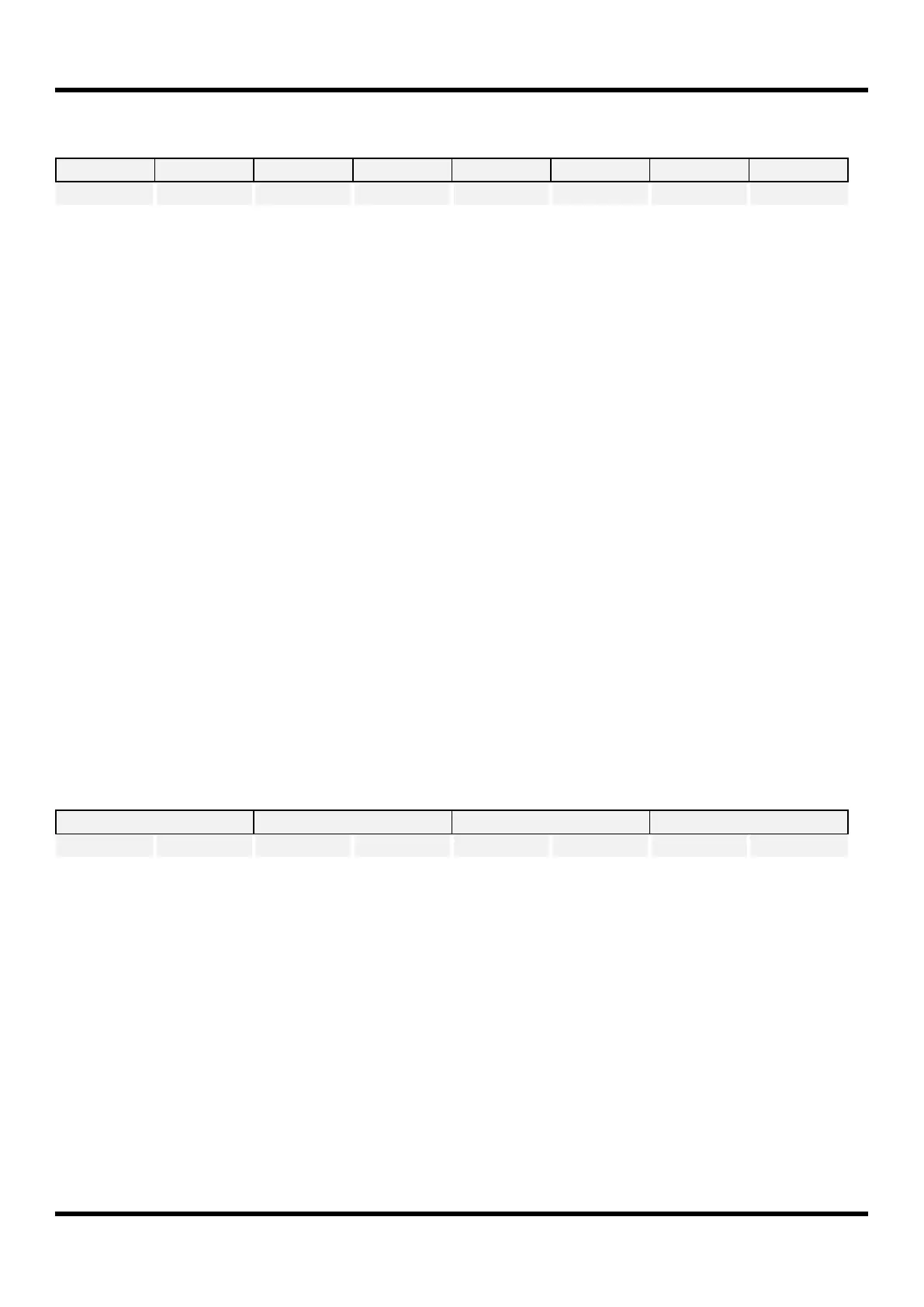

EIFLAG1 (External Interrupt Flag 1 Register): BBH

Initial value: 00H

When T7 interrupt occurs, this bit becomes ‘1’. The flag is cleared only by writing a ‘0’

to the bit. So, the flag should be cleared by software. Writing “1” has no effect.

T7 Interrupt no generation

When T6 interrupt occurs, this bit becomes ‘1’. The flag is cleared only by writing a ‘0’

to the bit. So, the flag should be cleared by software. Writing “1” has no effect.

T6 Interrupt no generation

When T5 interrupt occurs, this bit becomes ‘1’. The flag is cleared only by writing a ‘0’

to the bit. So, the flag should be cleared by software. Writing “1” has no effect.

T5 Interrupt no generation

When T4 interrupt occurs, this bit becomes ‘1’. The flag is cleared only by writing a ‘0’

to the bit. So, the flag should be cleared by software. Writing “1” has no effect.

T4 Interrupt no generation

When T3 interrupt occurs, this bit becomes ‘1’. The flag is cleared only by writing a ‘0’

to the bit. So, the flag should be cleared by software. Writing “1” has no effect.

T3 Interrupt no generation

When an External Interrupt 8/9/18(EINT8, EINT9, EINT18) is occurred, the flag

becomes ‘1’. The flag is cleared by writing a ‘0’ to the bit. So, the flag should be

cleared by software. Writing “1” has no effect.

External Interrupt 8/9/18 not occurred

External Interrupt 8/9/18 occurred

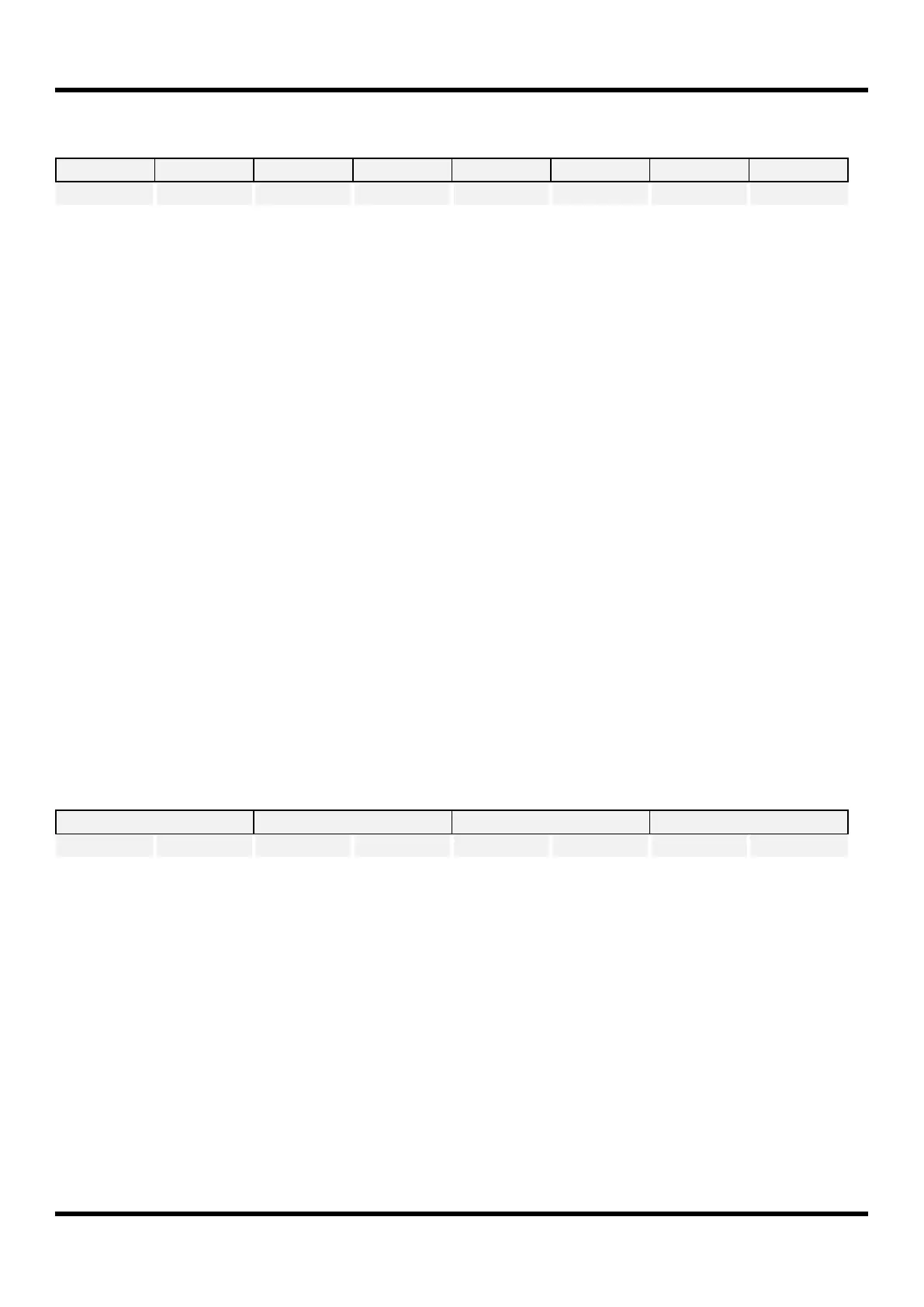

EIPOL1 (External Interrupt Polarity 1 Register): BFH

Initial value: 00H

External interrupt (EINT8,EINT9,EINT18) polarity selection

Interrupt on falling edge

Interrupt on both of rising and falling edge

Loading...

Loading...