188

ABOV Semiconductor Co., Ltd.

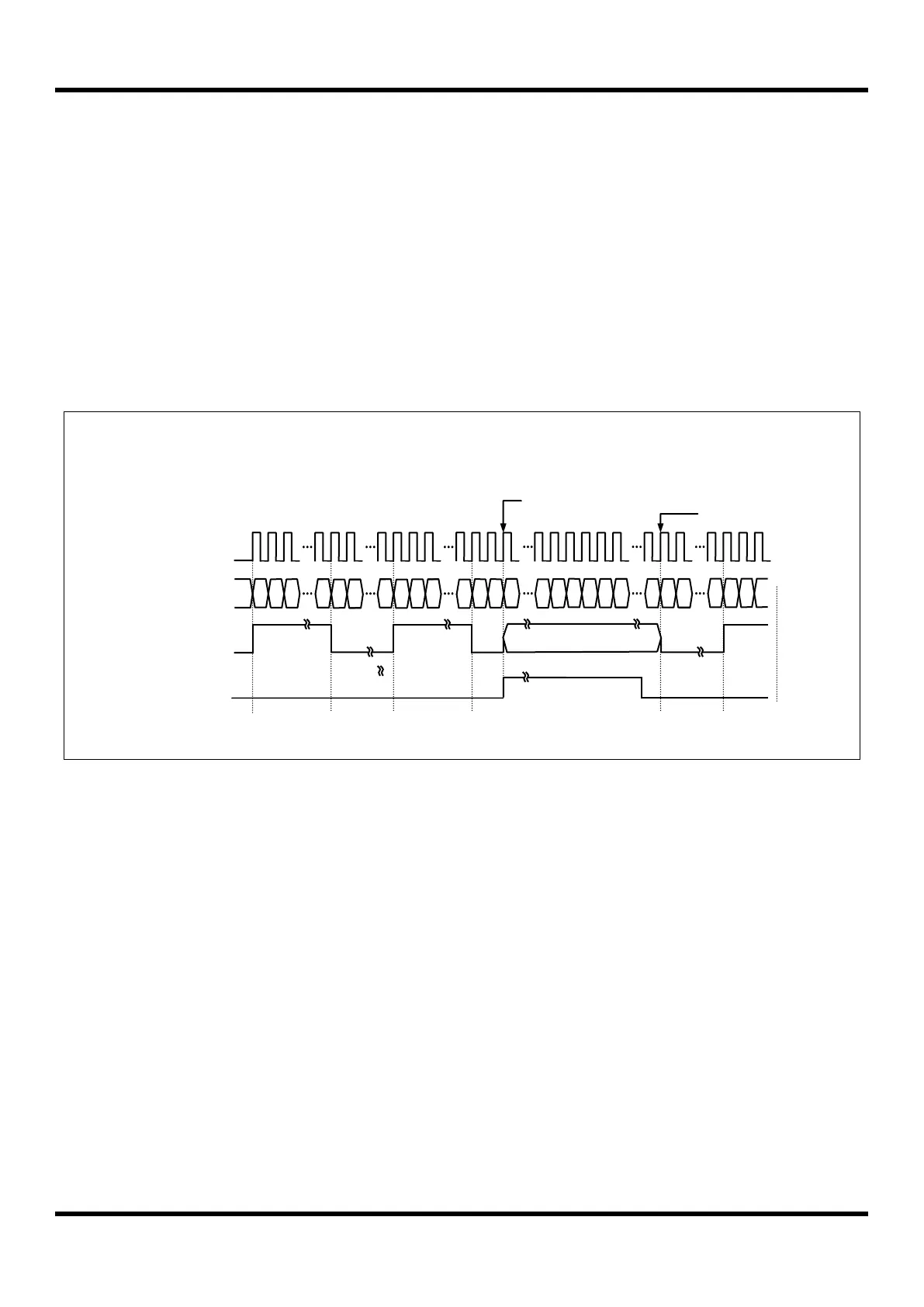

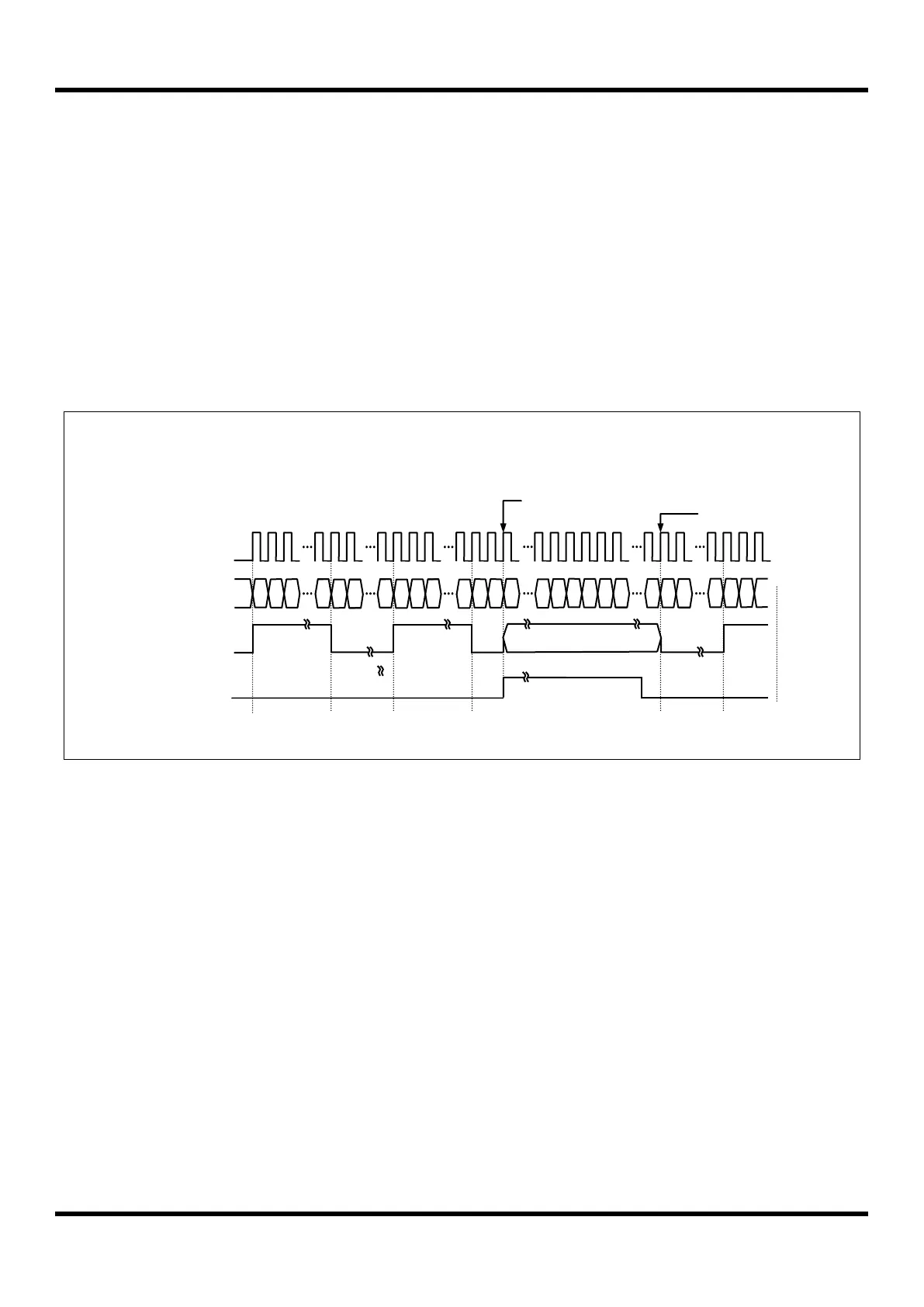

External Sync

If using ESYNC bit of T8PCR1 register, it is possible to synchronize the output of PWM from external signal.

If ESYNC bit sets to ‘1’, the external signal moves to PWM module through the BLNK pin. If BLNK signal is on rising

edge, immediately PWM output become HIGH-Z. Then HZCLR bit set ‘1’ PWM output is normally generated. (Figure

11.34 referred)

PWM Halt

If using PHLT bit of T8PCR1 register, it is possible to stop PWM operation by the software. During PHLT bit being ‘1’,

PWM output becomes a reset value and internal counter becomes reset as 0. Without changing PWM setting,

temporarily it is able to stop PWM. In case of T8CNT, when stopping counter, PWM output pin remains before states.

But if PHLT bit sets to ‘1’, PWM output pin has reset value.

Figure 11.34 Example of PWM External Synchronization with BLNK Input

T8PCR1 = 40

H

(EYNC=1)

T8PPRH = 00

H

T8PPRL = 2A

H

T8ADRH = 00

H

T8ADRL = 12

H

BLNK “1”

PWM OUTPUT

HIGH-Z

HZCLR “1”

PWM Release

HIGH-Z

Loading...

Loading...