49

8331B–AVR–03/12

Atmel AVR XMEGA AU

ule is enabled. This reduces the peak current consumption during startup of the module. For

maximum effect the start-up delay should be set so that it is larger than 0.5µs.

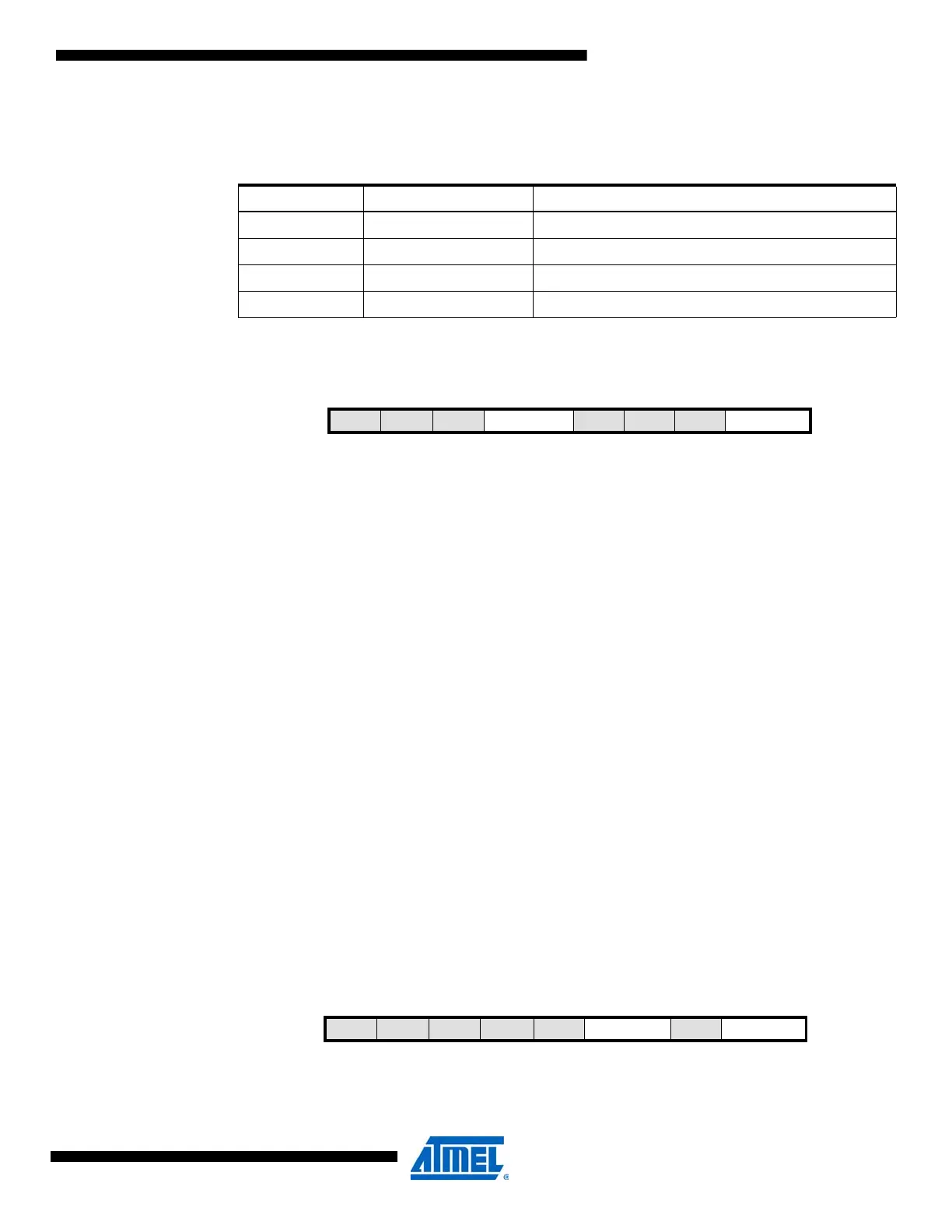

4.20.8 EVSYSLOCK – Event System Lock register

• Bit 7:5 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 4 – EVSYS1LOCK:

Setting this bit will lock all registers in the event system related to event channels 4 to 7 for fur-

ther modification. The following registers in the event system are locked: CH4MUX, CH4CTRL,

CH5MUX, CH5CTRL, CH6MUX, CH6CTRL, CH7MUX, CH7CTRL. This bit is protected by the

configuration change protection mechanism. For details refer to ”Configuration Change Protec-

tion” on page 13.

• Bit 3:1 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 0 – EVSYS0LOCK:

Setting this bit will lock all registers in the event system related to event channels 0 to 3 for fur-

ther modification. The following registers in the event system are locked: CH0MUX, CH0CTRL,

CH1MUX, CH1CTRL, CH2MUX, CH2CTRL, CH3MUX, CH3CTRL. This bit is protected by the

configuration change protection mechanism. For details refer to ”Configuration Change Protec-

tion” on page 13.

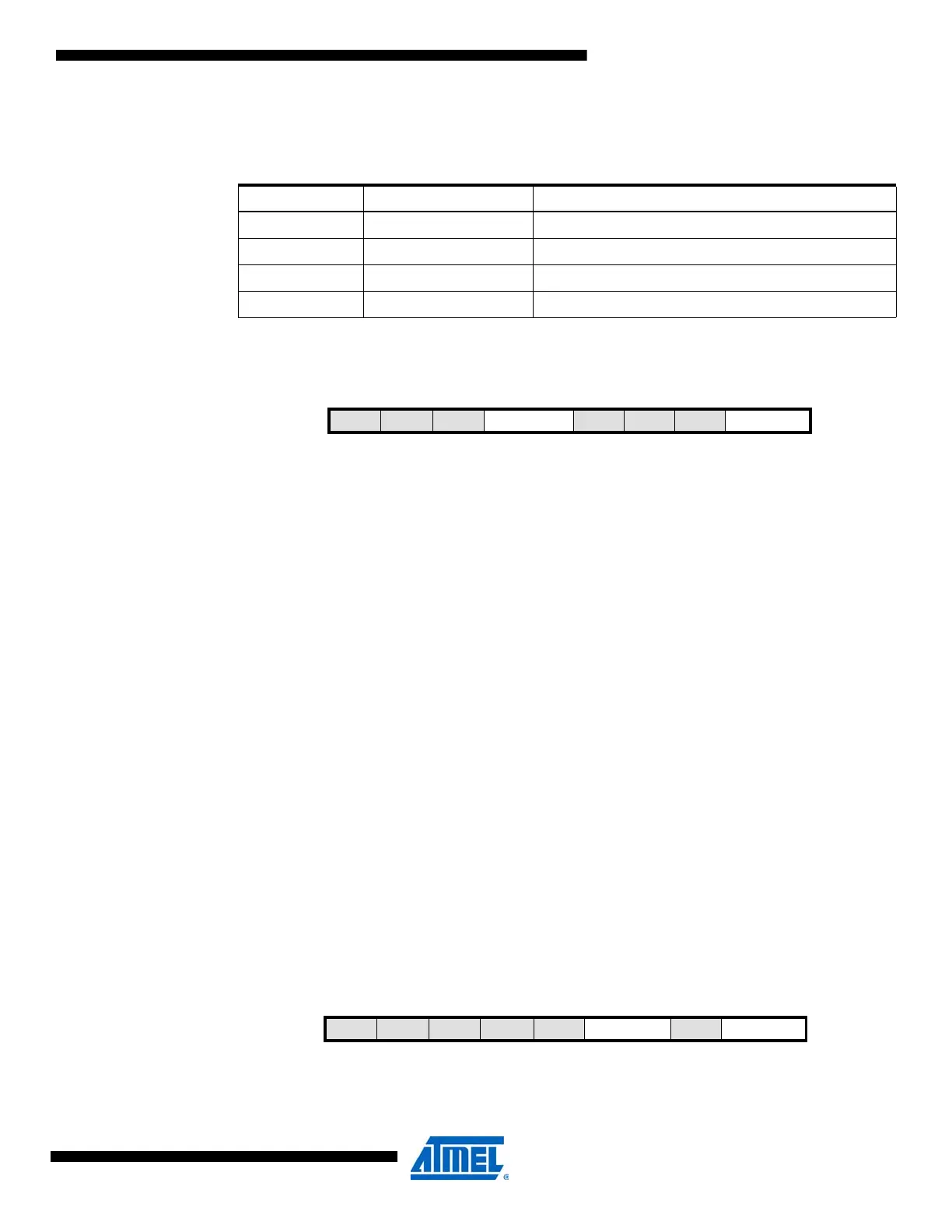

4.20.9 AWEXLOCK – Advanced Waveform Extension Lock register

Table 4-13. Analog startup delay.

STARTUPDLYx Group Configuration Description

00 NONE Direct startup

11 2CLK 2 * CLK

PER

10 8CLK 8 * CLK

PER

11 32CLK 32 * CLK

PER

Bit 765 4 321 0

+0x08 – – – EVSYS1LOCK – – – EVSYS0LOCK EVSYSLOCK

Read/Write R R R R/W R R R R/W

Initial Value 0 0 0 0 0 0 0 0

Bit 76543 2 1 0

+0x09

– – – – – AWEXELOCK – AWEXCLOCK AWEXLOCK

Read/Write RRRRR R/W R R/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...