6-40

Guidelines

WARNING!

The DIMMs are not hot swappable.

You can install a maximum of 12 DIMMs for each processor, six DIMMs per memory controller. For

more information, see "DIMM slots."

For a DIMM to operate at 2933 MHz, make sure the following conditions are met:

• Use Cascade Lake processors that support 2933 MHz data rate.

• Use DIMMs with a maximum of 2933 MHz data rate.

• Install only one DIMM per channel.

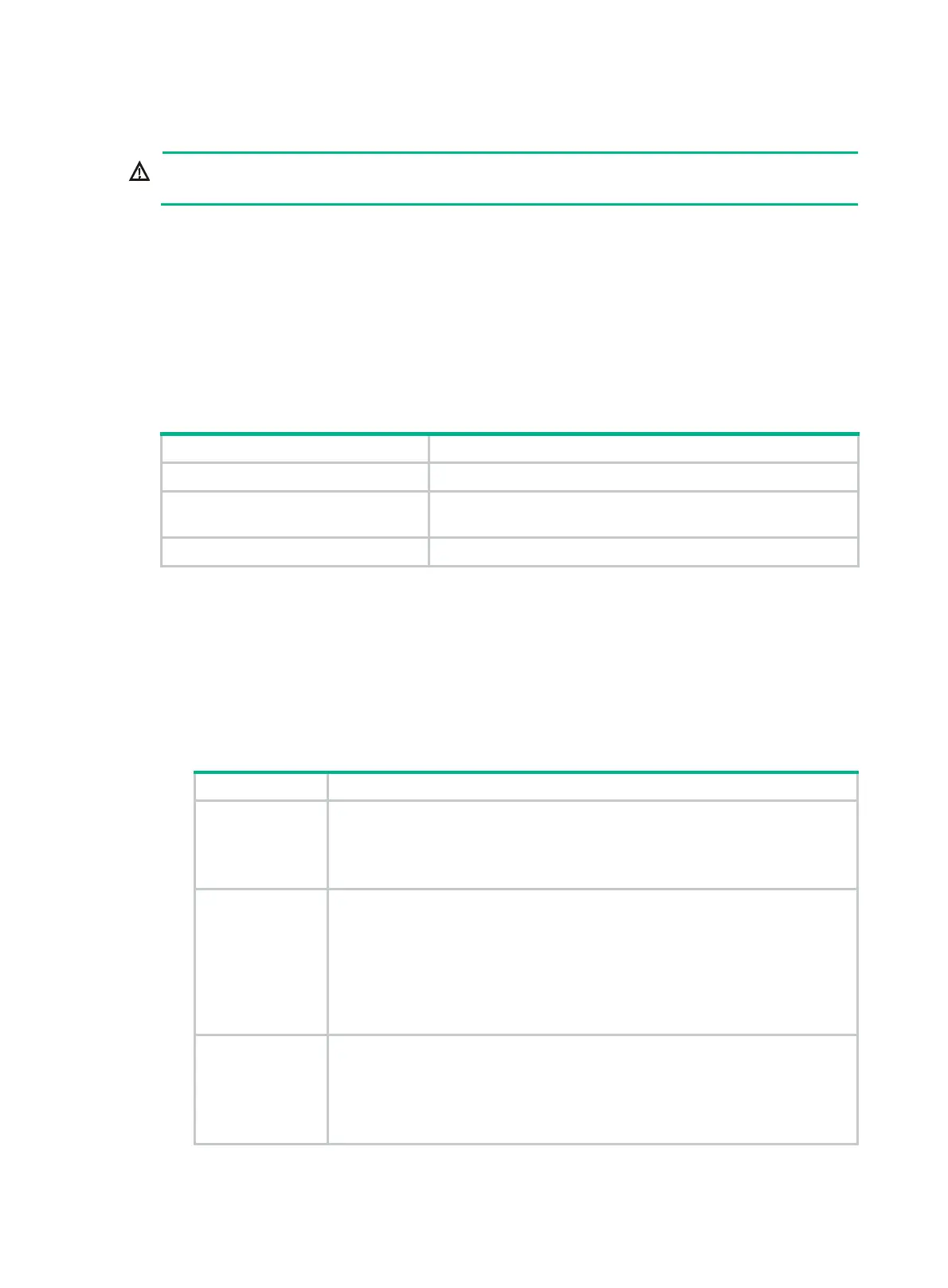

The supported DIMMs vary by processor model, as shown in Table 6-3.

Table 6-3

Supported DIMMs of a processor

Processor Supported DIMMs

Skylake Only DRAM DIMMs.

Cascade Lake

• Only DRAM DIMMs.

• Mixture of DCPMM and DRAM DIMMs.

Jintide-C series Only DRAM DIMMs.

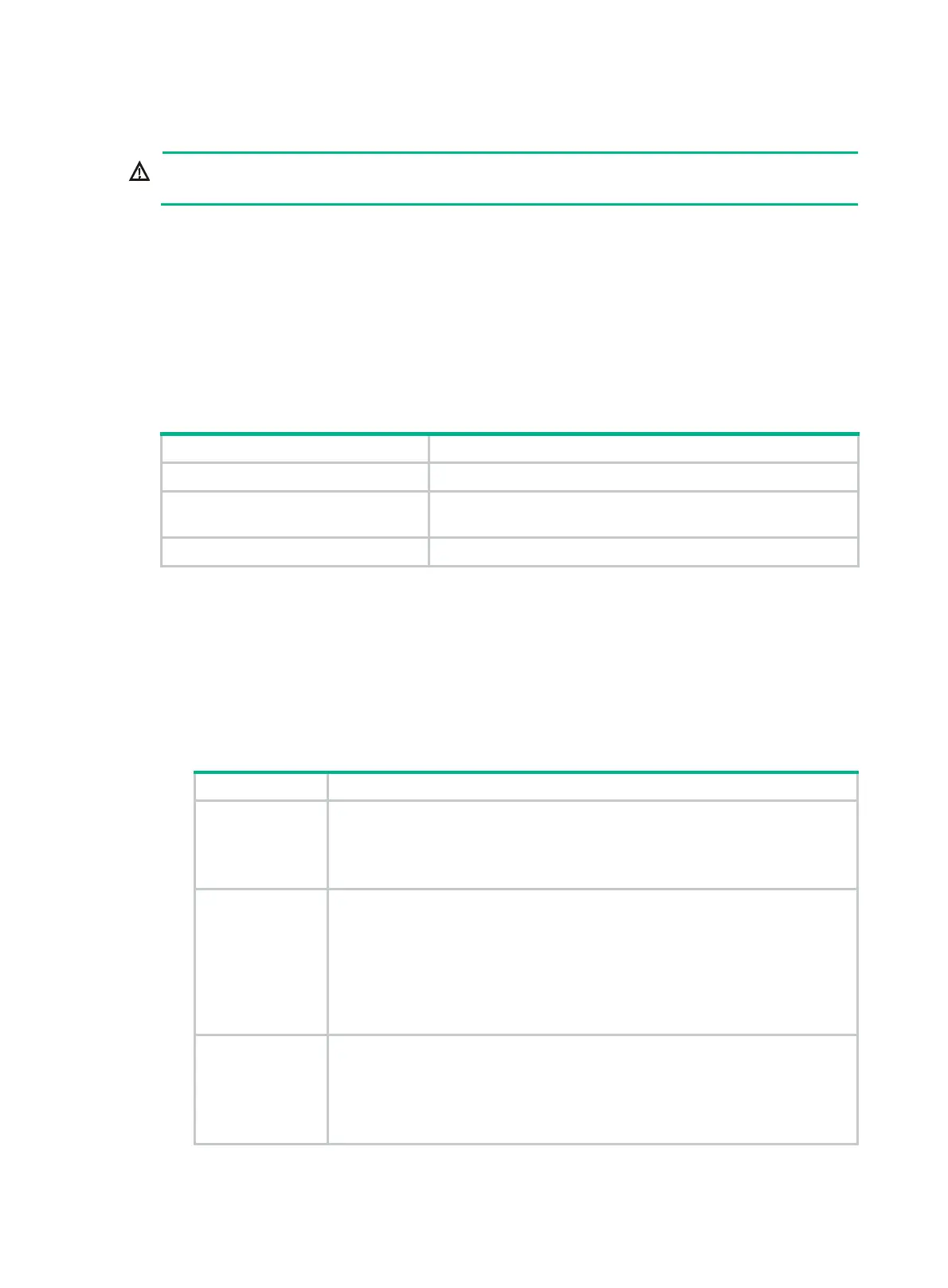

Guidelines for installing only DRAM DIMMs

When you install only DRAM DIMMs, follow these restrictions and guidelines:

• Make sure all DRAM DIMMs installed on the server have the same specifications.

• Make sure the corresponding processor is present before powering on the server.

• Make sure the number of ranks per channel does not exceed eight.

• For the memory mode setting to take effect, make sure the following installation requirements

are met when you install DRAM DIMMs for a processor:

Memory mode DIMM requirements

Independent

• If only one processor is present, see Figure 6-47.

•

If two processors of model 6xxx or 8xxx are present, see Figure 6-48.

•

If two processors of model 5xxx are present, see Figure 6-49.

• If four processors are present, see Figure 6-50.

Mirror

Partial Mirror

• A minimum of two DIMMs for a processor.

• This mode does not support DIMM population schemes that are not

recommended in Figure 6-47, Figure 6-48, Figure 6-49, an

d Figure 6-50.

• If only one processor is present, see Figure 6-47.

• If two processors of model 6xxx or 8xxx are present, see Figure 6-48.

• If two processors of model 5xxx are present, see Figure 6-49.

• If four processors are present, see Figure 6-50.

Memory Rank

Sparing

• A minimum of 2 ranks per channel.

• If only one processor is present, see Figure 6-47.

•

If two processors of model 6xxx or 8xxx are present, see Figure 6-48.

• If two processors of model 5xxx are present, see Figure 6-49.

•

If four processors are present, see Figure 6-50.

Loading...

Loading...