i~o

MCS@-51 ARCHITECTURAL OVERVIEW

but the stack itself is accessed by indirect addressing

using the SP register. This means the stack can go into

the Upper 128, if they are implemented, but not into

SFR space.

In devices that do not implement the Upper 128,if the

SP points to the Upper 128,PUSHed bytes are lost, and

POPped bytes are indeterminate.

The Data Transfer instructions include a id-bit MOV

that can be used to initialise the Data Pointer (DPTR)

for look-up tables in Program Memory, or for Id-bit

external Data Memory accesw.

The XCH A, <byte> instruction causes the Amu-

lator snd addressed byte to exchsnge data. The

XCHD

A,@Ri instruction is similar, but only the low nibbles

are involved in the exchange.

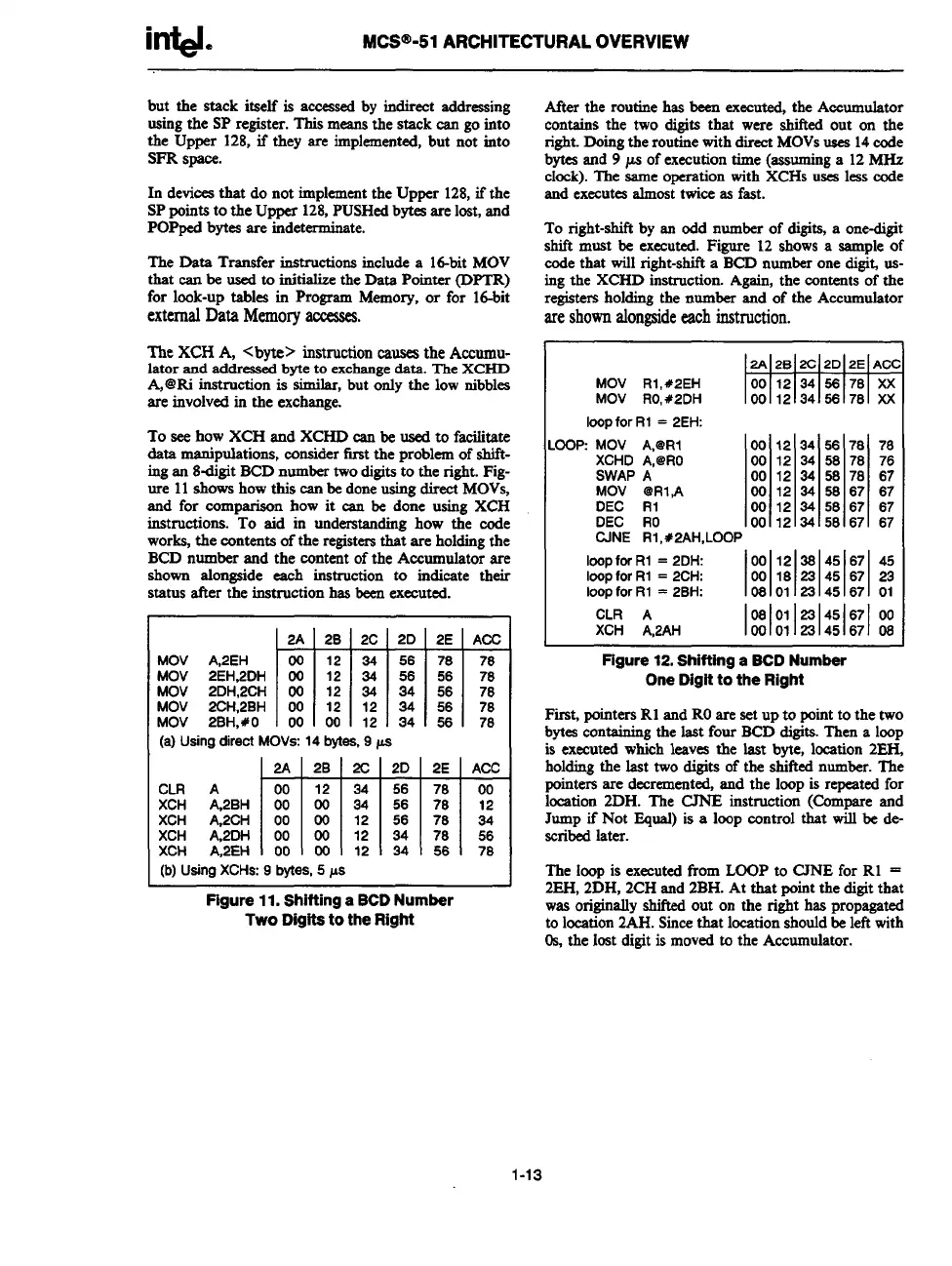

To see how XCH and XCHD can be used to fatitate

data manipulations, consider first the problem of shit%-

ing an 8digit BCD number two digits to the right. Fig-

ure 11 shows how this can be done using direct MOVS,

and for comparison how it can be done using XCH

instructions. To aid in understanding how the code

works, the contents of the registers that are holding the

BCD number and the content of the Accumulator are

shown alongside each instruction to indicate their

status after the instruction has been executed.

n3JMm

MOV A,2EH

MOV 2EH2DH % ;; : % ~

MOV 2CH:2BH 00 12

(a) Using direct MOVS 14 bytes, 9 ps

~

gm

(b) Using XCHS 9 bytes, 5 ps

. .

Figure 11. Shifting a BCD Number

Two Dlgite to the Right

Atler the routine has been executed, the Accumulator

contains the two digits that were shitled out on the

right. Doing the routine with direct MOVSuses 14code

bytes and 9 ps of execution time (assuming a 12 MHs

clock). The same operation with XCHS uses less code

and executes almost twice as fast.

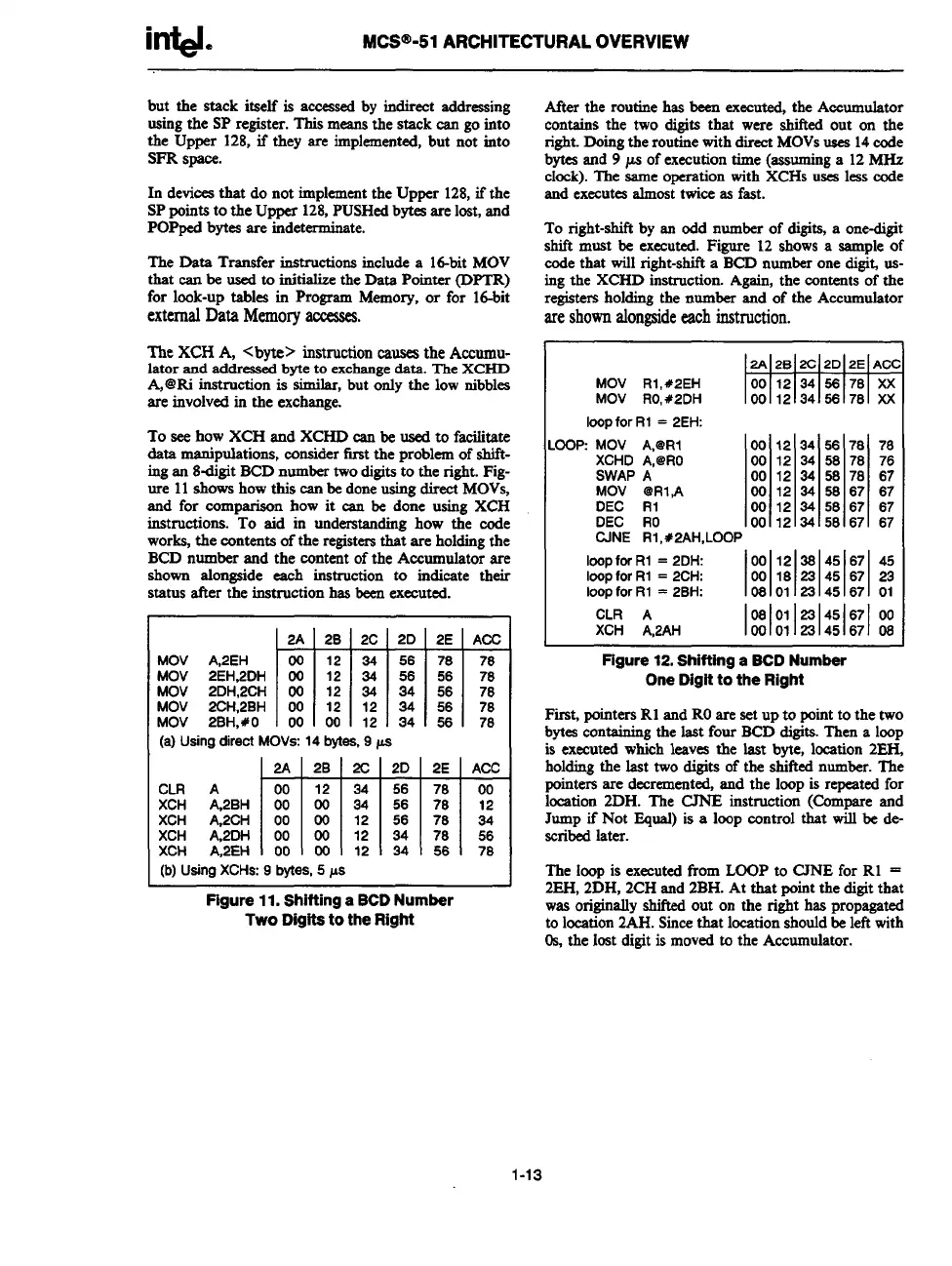

To right-shift by an odd number of digits, a one-digit

shift must be executed. Figure 12 shows a sample of

code that will right-shii a BCD number one digi~ us-

ing the XCHD instruction. Again, the contents of the

registers holding the number and of the Accumulator

areshownalongsideeachinstruction.

MOV Rl, #2EH

MOV RO,#2DH

m

loop for R1 = 2EH

.00P MOV A,@Rl 00 12 34 56 78 76

XCHD A,@RO

00 12 34 56 78 76

SWAP A

00 12 34 58 78 67

MOV @Rl,A

00 12 34 58 67 67

DEC RI

00 12 34 58 67 67

DEC RO

00 12 34 56 67 67

CJNE Rl,#2AH,LOOP

Imp for RI = 2DH

00 12 36 45 67 45

loop for R1 = 2CH:

00 18 23 45 67 23

ioop for RI = 2BH:

0s

01 22 45 67 01

CLR A

06

01 23 45 67 00

XCH A,2AH

00 01 23 45 67 06

Figure 12. Shifting a SCD Number

One Digit to the Right

First, pointers RI and ROare setup to point to the two

bytea containing the last four BCD digits. Then a loop

is executed which leaves the last byte, location 2EIL

holding the last two digits of the shifted number. The

pointers are decrernented, and the loop is repeated for

location 2DH. The CJNE instruction (Compare and

Jump if Not Equal) is a loop control that will be de-

scribed later.

The loop is executed from LOOP to CJNE for R1 =

2EH, 2DH, 2CH and 2BH. At that point the digit that

was originally shii out on the right has propagated

to location 2AH. Siice that location should be left with

0s, the lost digit is moved to the Accumulator.

1-13

Loading...

Loading...