in~o

87C51GBHARDWARE DESCRIPTION

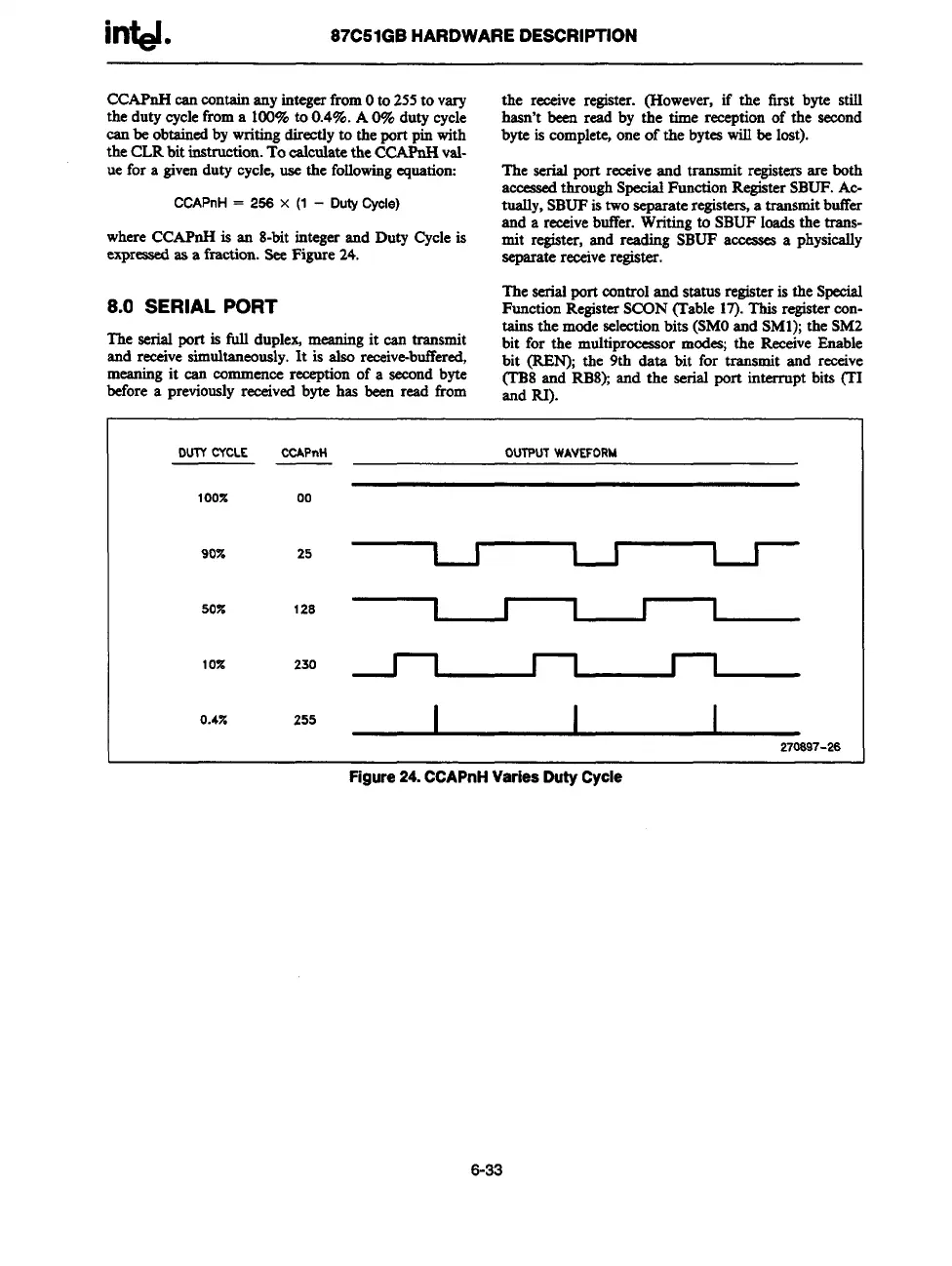

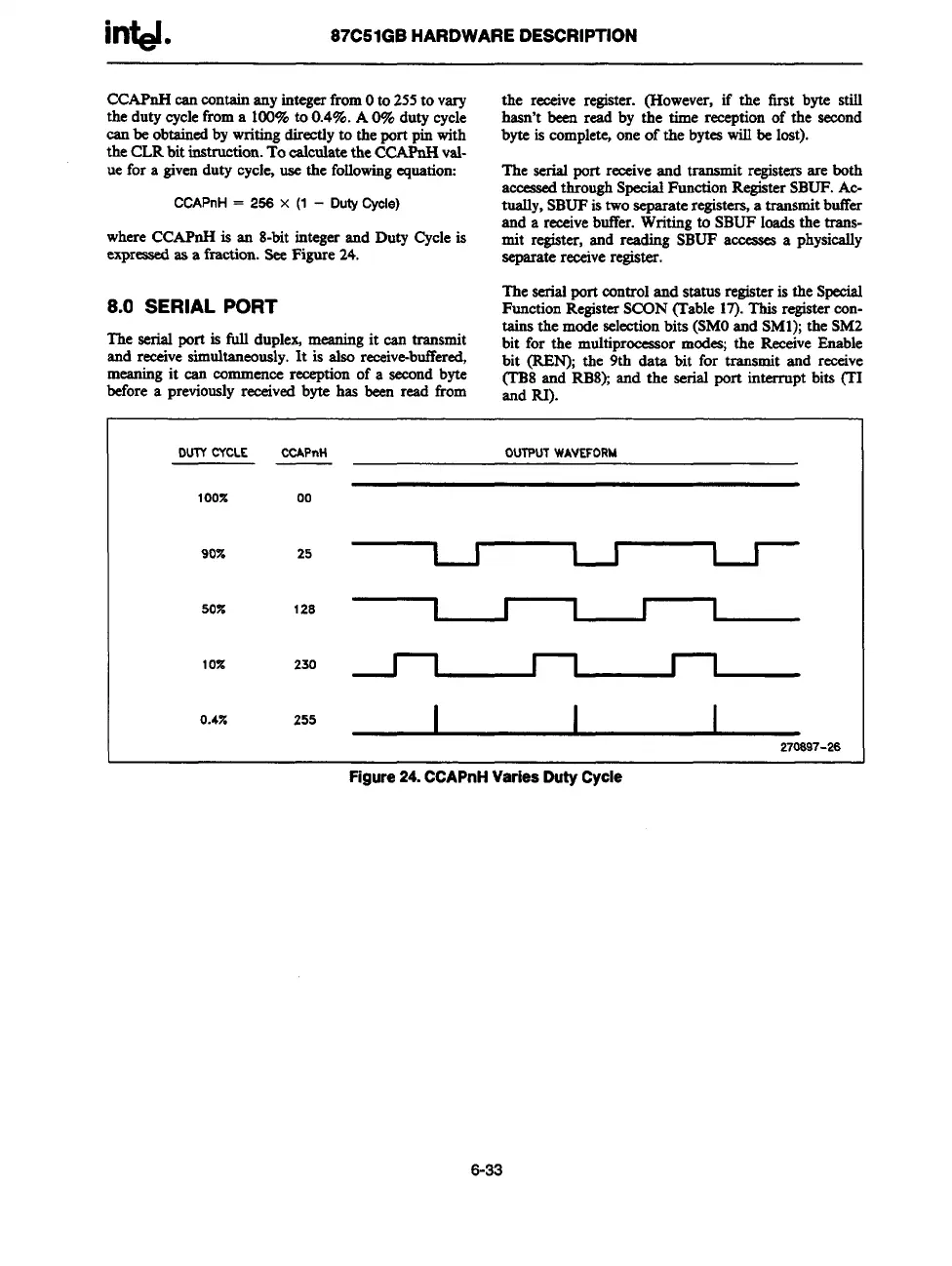

CCAPnHcancontainany integerfromOto255to vary

the dutycyclefroma 100%to 0.4%. A

0%0 dutycycle

canbe obtainedby writingdirectlyto the port pinwith

the CLRbit instruction.To calculatethe CCAPnHval-

ue for a givenduty cycle,w the followingequation:

CCAPnH= 256x (1- DutyCycle)

whereCCAPUHis an 8-bit integerand Duty Cycleis

expressedas a fraction. SeeFigure24.

8.0 SERIALPORT

The serial port is full duple~ meaningit can transmit

and receivesimultaneously.lt is also receive-buffered,

meaningit can commencereceptionof a secondbyte

before a previouslyreceivedbyte has been read horn

the receive register. (However, if the first byte still

hasn’t been read by the time reception of the second

byteis complete,one of the byteswillbe lost).

The serial port receiveand transm

it registersare both

accessedthroughSpecialFunctionRegisterSBUF.Ac-

tually,SBUFistwoseparateregistera,a transmitbut%r

and a receivebuffer.Writingto SBUFloadsthe trans-

mit register, and reading SBUFaccessesa physically

separatereceiveregister.

Theserialport cantrol and status registeris the Special

FunctionRegisterSCK)Ncable 17).This registercxm-

tains the modeselectionbits (SMOand SM1);the SM2

bit for the multiprocess

or modes;the ReceiveEnable

bit (REN); the 9th data bit for transmit and receive

(TB8and RB8);and the serial port interrupt bits (T1

and RI).

Din-f CYCLE

CCAPnH

OUTPUT WAVEFORM

100% 00

90%

50%

128 ~

10%

0.4%

255 ~

270697-26

Figure24.CCAPnHVeriesDutyCycle

6-33

Loading...

Loading...