intd.

83C152 HARDWARE DESCRIPTION

In an unnumbered fraroq information of variable

length may followthe control field if UI is used, or

information of fixed length may follow if FRMR is

used.

As stated earlier,the usersoftwareis responsiblefor the

propermanagementofthe controlfield.Thisportionof

the frame is passedto or fromthe GSCFIFOSas basic

informationaltypedata.

INFO - ‘lMsis

theinformationfieldand containsthe

data that onedeviceon the link wishesto transmit to

another device.It canbe ofany lengththe user wishesj

but mustbea multipleof 8bits. It is possiblethat some

ffamesmay containno informationfield.The informa-

tion field is identifiedto the receivingstations by the

preceding control field and the followingCRC. The

GSCdetermineswherethe last of the informationfield

is by passing the bits through the CRC generator.

When the last bit or EOF is receivedthe bits that re-

main constitutethe CRC.

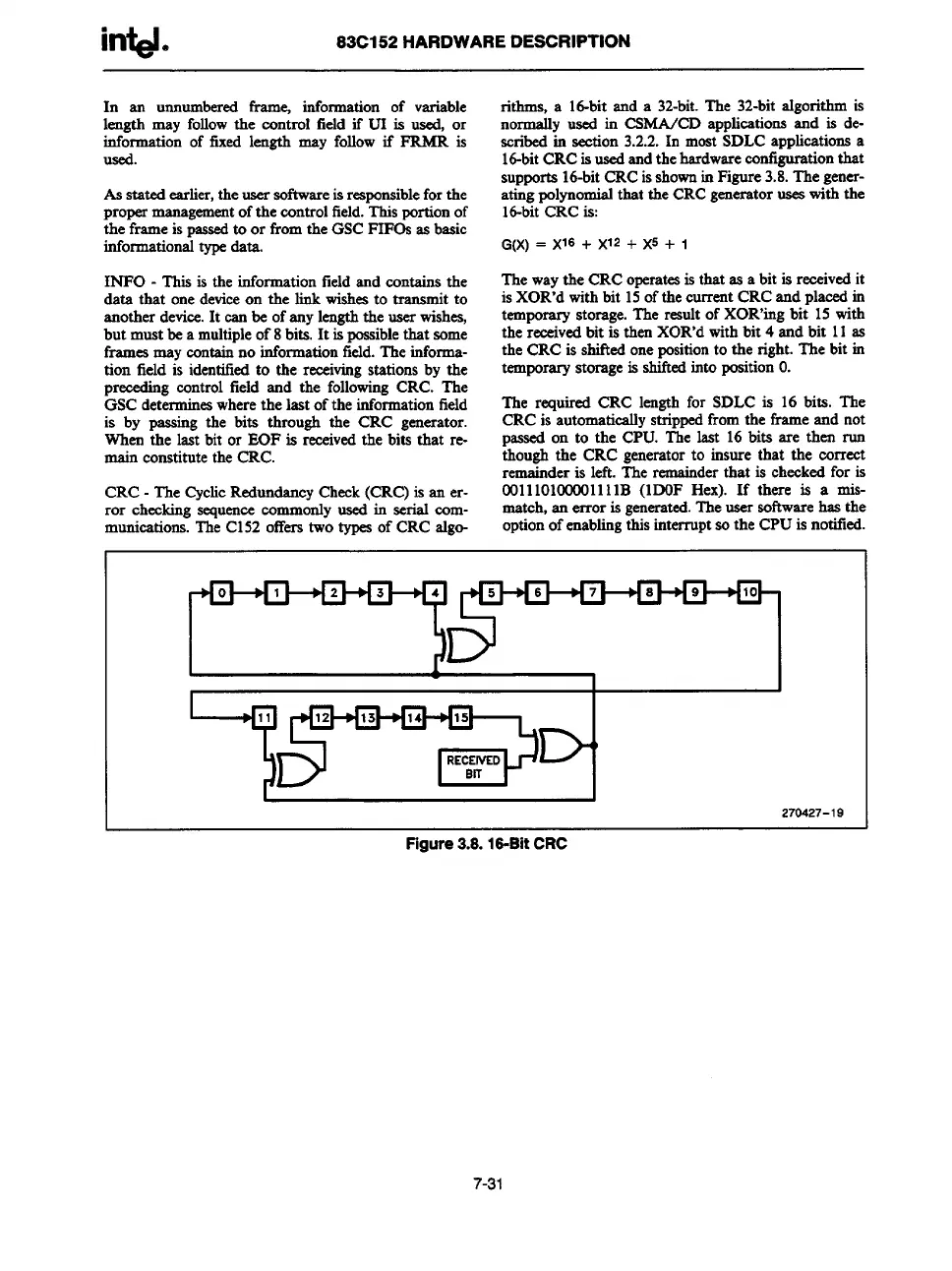

CRC - The CyclicRedundancyCheck(CRC)is an er-

ror checkingsequencecommonlyused in serial comm-

unications. TheC152offerstwo types of CRC algo-

rithms, a 16-bitand a 32-bit.The 32-bitalgorithm is

normally used in CSMA/CD applicationsand is de-

scribedin section 3.2.2.In mostSDLCapplicationsa

16-bitCRC is usedandthehardwareconfigurationthat

supporta16-bitCRCisshownin Figure3.8.The gener-

atingpolynomialthat the CRCgeneratoruseswith the

16-bitCRC is:

G(X)= x16+ X12+ X5+ 1

Thewaythe CRCoperatesis that as a bit is receivedit

is XOR’dwithbit 15ofthe current CRC and placedin

temporarystorage.The resultof XOR’ingbit 15with

the receivedbit is then XOR’dwithbit 4 and bit 11as

the CRC is shitledonepositionto the right. The bit in

temporaryatorageis shiftedintopositionO.

The required CRC length for SDLC is 16 bits. The

CRCis automaticallystrippedfromthe frame and not

passedon to the CPU. The last 16bits are then run

though the CRC generatorto insure that the correct

remainderis left. The remainderthat is checkedfor is

00111010000111lB (lDOF Hex). If there is a mis-

match,an error is generated.Theuser softwarehas the

optionof enablingthisinterruptso the CPUis notified.

“g?-’yq+

270427-19

Figure 3.8. 15-Bit CRC

7-31

Loading...

Loading...